# Public

# Infineon Technologies AG Security and Chipcard ICs

**Evaluation Documentation**

# SLE66C166PE / m1532-a24

**Security Target**

Version 1.0 Date 2005-08-16 Author H.-J. Novinsky, H.-U. Buchmüller

Filename: SLE66C166PE\_SecurityTarget\_01

Ó2005 Infineon Technologies AG. All rights reserved. This document and all information contained therein is considered confidential and proprietary of Infineon technologies AG. The recipient of this document shall not disclose this document or the information contained herein in whole or in part to any third party. Infineon technologies AG reserves the right to change the specification or parts of it without prior notice.

# **REVISION HISTORY**

2005-08-16

Initial Version

# TABLE OF CONTENTS

| 1 | INTRO          | DUCTION                                      |        |       |            |       | 4    |

|---|----------------|----------------------------------------------|--------|-------|------------|-------|------|

|   | 1.1 S          | ECURITY TARGET IDENTIFICATION                |        |       |            |       | 4    |

|   |                | ECURITY TARGET OVERVIEW                      |        |       |            |       |      |

|   |                |                                              |        |       |            |       |      |

| ~ |                |                                              |        |       |            |       |      |

| 2 | DESC           | RIPTION OF THE TARGET OF EVALUATION          | (TOE)  | ••••• |            | ••••• | 6    |

|   | 2.1 P          | PRODUCT TYPE                                 |        |       |            |       | 6    |

|   | 2.2 S          | COPE OF THE TOE                              |        |       |            |       |      |

|   | 2.2.1          | Hardware of the TOE                          |        |       |            |       |      |

|   | 2.2.2          | Firmware and software of the TOE             |        |       |            |       |      |

|   | 2.2.3          | Guidance documentation                       |        |       |            |       |      |

|   | 2.2.4          | Forms of delivery                            |        |       |            |       |      |

|   | 2.2.5          | Production sites                             |        |       |            |       | 10   |

| 3 | TOE S          | SECURITY ENVIRONMENT                         |        |       |            |       | 11   |

|   | 3.1 D          | DEFINITION OF ASSETS                         |        |       |            |       | 11   |

|   |                | SSUMPTIONS                                   |        |       |            |       |      |

|   |                | HREATS                                       |        |       |            |       |      |

|   |                | REATORING SECURITY POLICIES                  |        |       |            |       |      |

|   | 3.4.1          | Augmented organisational security policy     |        |       |            |       |      |

| 4 | SECU           | RITY OBJECTIVES                              |        |       |            |       |      |

| 4 |                |                                              |        |       |            |       |      |

|   |                | ECURITY OBJECTIVES FOR THE TOE               |        |       |            |       |      |

|   |                | ECURITY OBJECTIVES FOR THE ENVIRONMENT       |        |       |            |       |      |

|   | 4.2.1<br>4.2.2 | Clarification of "Usage of Hardware Platform |        |       |            |       |      |

|   |                | Clarification of "Treatment of User Data (OE | • •    | • /   |            |       |      |

| 5 | IT SEC         | CURITY REQUIREMENTS                          |        |       |            |       | 16   |

|   | 5.1 T          | OE SECURITY REQUIREMENTS                     |        |       |            |       | 16   |

|   | 5.1.1          | TOE security functional requirements         |        |       |            |       |      |

|   | 5.1.2          | TOE security assurance requirements          |        |       |            |       |      |

|   | 5.1.3          | Refinements                                  |        |       |            |       |      |

|   |                | ECURITY REQUIREMENTS FOR THE ENVIRONMENT     |        |       |            |       |      |

|   | 5.2.1          | Security requirements for the IT Environmer  |        |       |            |       |      |

|   | 5.2.2          | Security Requirements for the Non-IT-Envir   | onment | ••••• |            |       |      |

| 6 | TOE S          | SUMMARY SPECIFICATION                        |        |       |            |       | 28   |

|   | 6.1 S          | EF1: OPERATING STATE CHECKING                |        |       |            |       |      |

|   |                | EF2: PHASE MANAGEMENT WITH TEST MODE LOCK    |        |       |            |       |      |

|   |                | EF3: PROTECTION AGAINST SNOOPING             |        |       |            |       |      |

|   | 6.4 S          | EF4: DATA ENCRYPTION AND DATA DISGUISING     |        |       |            |       | 29   |

|   |                | EF5: RANDOM NUMBER GENERATION                |        |       |            |       |      |

|   |                | EF6: TSF SELF TEST                           |        |       |            |       |      |

|   |                | EF7: NOTIFICATION OF PHYSICAL ATTACK         |        |       |            |       |      |

|   |                | EF8: MEMORY MANAGEMENT UNIT (MMU)            |        |       |            |       |      |

|   |                | EF9: CRYPTOGRAPHIC SUPPORT                   |        |       |            |       |      |

|   |                | APPING OF SECURITY FUNCTIONAL REQUIREMENT    |        |       |            |       |      |

|   | 6.11 A         | SSURANCE MEASURES                            |        |       |            |       |      |

| 7 | PP CL          | _AIMS                                        |        |       |            |       | 34   |

|   | 7.1 P          | P REFERENCE                                  |        |       |            |       | 34   |

|   |                | P TAILORING                                  |        |       |            |       |      |

|   | 7.2.1          | FCS_RND                                      |        |       |            |       | 34   |

|   |                |                                              | V1 0   | Date: | 2005-08-16 | Page: | 2/46 |

| 1 |                |                                              |        | u.u.  |            |       | _,   |

Infineon

|    | 7.3 | PP ADDITIONS                                                                    |    |

|----|-----|---------------------------------------------------------------------------------|----|

| 8  | R   | ATIONAL                                                                         | 35 |

|    | 8.1 | SECURITY OBJECTIVES RATIONALE                                                   |    |

|    | 8.2 | SECURITY REQUIREMENTS RATIONALE                                                 |    |

|    | 8.  | 2.1 Rationale for the security functional requirements                          |    |

|    | 8.  | 2.2 Dependencies of security functional requirements                            |    |

|    | 8.  | 2.3 Rationale for the Assurance Requirements and the Strength of Function Level |    |

|    | 8.3 | SECURITY REQUIREMENTS ARE MUTUALLY SUPPORTIVE AND INTERNALLY CONSISTENT         | 41 |

| 9  | R   | EFERENCES                                                                       | 42 |

|    | 9.1 | DOCUMENTS AND USER GUIDANCE                                                     |    |

|    | 9.2 | LITERATURE                                                                      |    |

|    | 9.3 | LIST OF ABBREVIATIONS                                                           |    |

|    | 9.4 | GLOSSARY                                                                        |    |

| 10 | )   | DEFINITION OF THE SECURITY FUNCTIONAL COMPONENT FPT_TST.2                       | 46 |

#### List of tables:

| Table 1: Identification                                                                       | 4    |

|-----------------------------------------------------------------------------------------------|------|

| Table 2: Basic TOE data                                                                       | 4    |

| Table 3: Memory organization and sizes                                                        | 6    |

| Table 4: Production site in chip identification                                               | . 10 |

| Table 5: Threats to Smartcards according to the Protection Profile                            | . 12 |

| Table 6: Objectives for Smartcards according to the Protection Profile                        | . 14 |

| Table 7: Additional objectives due to TOE specific functions and augmentations                | . 14 |

| Table 8: Security objectives for the environment                                              | . 14 |

| Table 9: Security functional requirements defined in Smartcard IC Platform Protection Profile | . 16 |

| Table 10: Augmented security functional requirements                                          | . 16 |

| Table 11: Assurance components                                                                | . 22 |

| Table 12: Mapping of SFR and SEF                                                              | . 31 |

| Table 13: Assurance measures                                                                  |      |

| Table 14: Security Objective Rational                                                         | . 35 |

| Table 15: Rational for cryptographic operation requirement                                    | . 36 |

| Table 16: Rational for subset TOE security testing requirement                                | . 37 |

| Table 17: Rational for Memory Access Control Policy requirement                               | 38   |

| Table 18: Rational for integrity check requirement                                            | 38   |

| Table 19: Rational for integrity check requirement                                            | 39   |

| Table 20: Dependency for cryptographic operation requirement                                  | 39   |

| Table 21: Dependency for subset TOE security testing requirement                              | 39   |

| Table 22: Dependency for Memory Access Control Policy requirement                             | . 40 |

| Table 23: Dependency for integrity monitoring requirements                                    | . 40 |

| Table 24: User guidance                                                                       | 42   |

| Table 25: Table of Criteria                                                                   | 42   |

V1.0 Date: 2005-08-16 Page: 3/46

# 1 Introduction

#### 1.1 Security Target Identification

The Security Target has the revision 1.0 and is dated 2005-08-16.

The Security Target is based on the Protection Profile "Smartcard IC Platform Protection Profile".

The Protection Profile and the Security Target are built with Common Criteria V2.1. The ST takes into account all relevant current final interpretations.

|                                          | Version number | Date        | Registration |

|------------------------------------------|----------------|-------------|--------------|

| Smartcard IC Platform Protection Profile | 1.0            | July 2001   | BSI-PP-0002  |

| Common Criteria                          | 2.1            | August 1999 | ISO15408     |

Table 1: Identification

#### **1.2 Security Target Overview**

The Target of Evaluation (TOE) is the product SLE66C166PE / m1532-a24 and will be referenced as the TOE in the further. The TOE has been realized in UCP technology. UCP is the abbreviation for Unified Channel Programming, which stands for an improved way of programming the non volatile memory. Using UCP technology provides major benefits:

- much faster block wise programming of the flash EEPROM

- the use of much less chip area

- the ability to integrate much larger memory sizes.

The architecture and concept is a port of the already well established, proven and successfully EAL5+ certified product SLE66CX322P / m1484 b14 and f18 and of the SLE66CX680PE / m1534 a13 currently being in the EAL5+ certification process. The TOE and the SLE66CX680PE, both based on the highly secure platform of the SLE66CX322P, have seen – apart from the optimization of the EEPROM – the equal additional improvements concerning security. With these improvements this TOE is even more prepared to master the security challenges of the future.

The TOE is a smart card IC (Security Controller) meeting the highest requirements in terms of performance and security. It is manufactured by Infineon Technologies AG in a 0.22  $\mu$ m CMOS technology. This TOE is intended to be used in smart cards for particularly security-relevant applications.

In comparison with the SLE66CX680PE this TOE has an additionally blocked ACE and comes consequently without the RSA2048 library. The TOE can be identified clearly by the chip ident.

The basic data of the TOE are listed in the following table:

| Tab | le 2: Ba | sic TOE o | data |

|-----|----------|-----------|------|

|     |          |           |      |

| Sales name  | Mask number | Design status | Fabrication site | Chip ident |

|-------------|-------------|---------------|------------------|------------|

| SLE66C166PE | M1532       | A24           | Dresden          | 95h        |

The TOE contains the RMS library providing some functionality via an API to the Smartcard Embedded Software and STS firmware for test purposes. The STS is implemented in a separated test-ROM being part of the TOE too.

| V1.0 | Date: 2005-08-16 | Page: 4/46 |

|------|------------------|------------|

Infineon

The firmware libraries RMS 2.5 and STS 55.0B.07 are implemented together with the Smartcard Embedded Software in the User-ROM mask. All other Smartcard Embedded Software does not belong to the TOE and is not subject of the evaluation.

The main security features implemented in the TOE are:

- a SAB 8051 compatible instruction set and some additional powerful instructions needed for smart card applications,

- data encryption according to single-DES and 3DES standard (single DES is out of scope of the evaluation),

- advanced security sensors and physical countermeasures (e.g. shielding),

- true random number generation (AIS31 compliant),

- control of access rights to the memory by the memory management unit (MMU),

- automatic error detection/correction of the NVM content (EDC, ECC)

- data encryption for all CPU external memories by the integrated Memory Encryption and Decryption (MED),

- encryption of the data transported over the bus to and from the security sensitive SFRs

- Countermeasures against SPA, DPA, EMA, and DFA attacks.

In this security target the TOE (target of evaluation) is described and a summary specification is given. The security environment of the TOE during its different phases of the lifecycle is defined. The assets are identified which have to be protected through the security policy. The threats against these assets are described. The security objectives as the objectives of the security policy are defined as well as the security requirements. The requirements are built up of the security functional requirements as part of the security policy and the security assurance requirements as the steps during the evaluation and certification to show the TOE meets its requirements. The functionality of the TOE to meet the requirements is described.

The assets, threats, security objectives and the security functional requirements are defined in the Smartcard IC Platform Protection Profile and are referenced here. These requirements build up a minimal standard common for all Smartcards.

The security enforcing functions are defined here in the security target as property of this specific TOE. Here it is shown how this specific TOE fulfils the requirements for the standard defined in the Protection Profile.

#### **1.3 CC Conformance**

This security target is conformant to Common Criteria V2.1 (ISO15408) part 2 extended, part 3 conformant and conformant to the Smartcard IC Platform Protection Profile. The assurance level is EAL5 augmented (EAL5+) with components ALC\_DVS.2, AVA\_MSU.3 and AVA\_VLA.4.

The security requirements of the TOE according to the Smartcard IC Platform Protection Profile are listed in Table 9. The augmented security functional requirements (see Table 10) are listed and described in section 5.1.

# 2 Description of the Target of Evaluation (TOE)

The TOE description helps to understand the specific security environment and the security policy. In this context the assets, threats, security objectives and security functional requirements can be employed. The following is a more detailed description of the TOE than in the Smartcard IC Platform Protection Profile as it belongs to the specific TOE.

#### 2.1 Product Type

The Target of Evaluation (TOE) comprises smart card ICs used as Security Controllers meeting the highest requirements in terms of performance and security. They are manufactured by Infineon Technologies AG in a 0.22  $\mu$ m CMOS technology. The controllers intended to be used in smart cards for particularly security-relevant applications. That is based on its previous use as developing platform for smart card operating systems according to the lifecycle model (in Smartcard IC Platform Protection Profile).

The term Smartcard Embedded Software is used in the following for all operating systems and applications stored and executed on the TOE. The TOE is the platform for the Smartcard Embedded Software. The Smartcard Embedded Software itself is not part of the TOE.

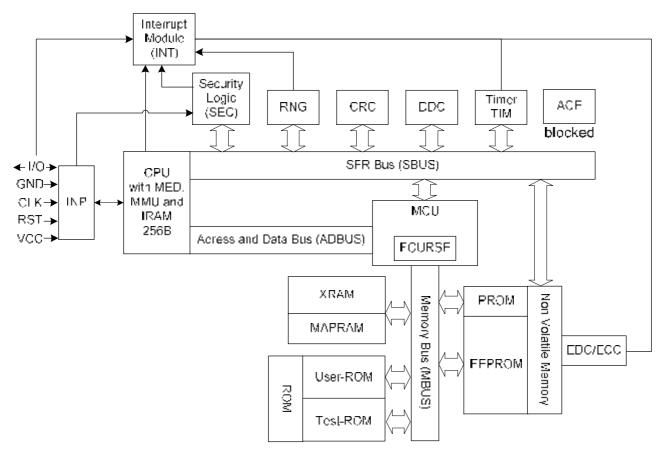

The TOE consists of a dedicated microprocessor (CPU) with a MMU (Memory Management Unit), several different memories, security logic, a timer and an interrupt-controlled I/O interface. A RNG (Random Number Generator) and a checksum module (CRC module) are integrated on the chip too. The related block diagram is shown in Figure 1.

The CPU in all variants is equal and is compatible with the SAB 8051 instruction set and is 6 times faster than the standard processor. It provides additional powerful instructions for smart card applications. The memory is organized and sized as listed in the following table:

| SLE66        | C166PE   |  |  |

|--------------|----------|--|--|

|              | m1532    |  |  |

| DesingStatus | a24      |  |  |

| XRAM         | 4k       |  |  |

| ROM          | 108k     |  |  |

| EEPROM       | 16k      |  |  |

| TestROM      | 12k      |  |  |

| UserROM      | 96k      |  |  |

| IRAM         | 256 byte |  |  |

| PROM         | 16 bytes |  |  |

| MapRAM       | 576x6bit |  |  |

| Chip ID -hex | 95       |  |  |

Table 3: Memory organization and sizes

The TOE thus meets the requirements of the new generation of operating systems. The CPU accesses the memory via the integrated Memory Encryption and Decryption unit (MED). The access rights of the application to the memories can be controlled with the memory management unit (MMU). Errors in the NVM are automatically detected/corrected by the EDC and ECC unit.

Security, sleep mode and interrupt logic as well as the RNG are specially designed for smart card applications. The sleep mode logic (clock stop mode per ISO/IEC 7816-3) is used to reduce the overall power consumption. The timer permits easy implementation of communication protocols such as T=1 and all other time-critical operations. The UART-controlled I/O interface allows the smart card and terminal to be operated in parallel. The VPLL (virtual PLL) unit allows operating all variants with a multiplication factor over the external clock signal or free running with maximum

| V1.0 Date: 2005-08-16 Page: 6/46 |

|----------------------------------|

|----------------------------------|

Infineon

frequency. The RNG does not supply a pseudorandom number sequence, but instead produces genuine random numbers under all conditions. The checksum module allows simple calculation of checksums per ISO 3309 (16 bit CRC).

The implemented "Dual Key DES and Cryptographic Unit Module" (DDC) performs cryptographic operations. This module computes the complete DES algorithm within a few clock cycles. That module is especially designed to counter attacks like DPA or EMA. The TOE includes functionality to calculate single DES operations but the evaluation includes only triple-DES operations.

The software (firmware) required for operating the chip consists of routines for programming the EEPROM from application programs and for online testing of the security enforcing functions. These are stored in a reserved user ROM area. In addition, the chip initialisation routine with security checks and identification mode as well as test routines for production testing are located in a separate test ROM.

There is new feature implemented described as Extended Configuration component CFG\_EXT which includes the extended SFR registers now being used for the general purposes and chip configuration. These registers are partly implemented as so called HWBITS.

HWBITS were introduced in order to be able to exchange the default settings of configuration registers to block certain modules or memory areas for so called blocked derivatives of the design. To achieve this, the configuration SFRs are not longer exclusively implemented as programmable registers being written in STS mode and then locked. The HWBITS used as extended SFR are hard-wired on the silicon now. This is implemented by special HWBIT0/HWBIT1 library cells in the semi-custom part (HardWiredBits). These cells are identified during the generation of the design data and replaced by appropriate HWBIT0 and HWBIT1 cells.

The TOE offers a new, improved standard of integrated security features, thereby meeting the requirements of all smart card applications such as information integrity, access control, mobile telephone, as well as uses in electronic funds transfer and healthcare systems.

To sum up, the TOE is a powerful smart card IC with a large amount of memory and special peripheral devices with both improved performance and optimised power consumption at minimal chip size. It therefore constitutes the basis for future smart card applications.

|  | V1.0 | Date: 2005-08-16 | Page: 7/4 |

|--|------|------------------|-----------|

|--|------|------------------|-----------|

Infineon

Figure 1: Block diagram of the TOE<sup>1</sup>

Please refer to Table 3 for the exact memory sizes by derivate.

#### 2.2 Scope of the TOE

The TOE comprises the *hardware* of chapter 1.1 listed smart card security controllers, manufactured by Infineon Technologies AG, and parts of the associated *firmware/software* required for operation. The documents described in section 2.2.3 and listed in Annex 9.1 are supplied as a manual. In the following description, the term "manufacturer" is an abbreviation for Infineon Technologies AG, the manufacturer of the TOE. The Smartcard Embedded Software is not part of the TOE.

#### 2.2.1 Hardware of the TOE

The *hardware part* of the TOE (see Figure 1) as defined in Smartcard IC Platform Protection Profile is comprised of:

- Security logic (SEC)

- Microcontroller type ECO 2000 (CPU) with the subcomponents memory encryption and decryption unit (MED), memory management unit (MMU) and 256 bytes of internal RAM (IRAM)

- Memory Control Unit (MCU) with FCURSE distributes the data to and from memory components while the FCURSE provides camouflage access operations

<sup>&</sup>lt;sup>1</sup> Note: This figure does not show the hardware bits providing extended configuration options, since they are used from various components and their implementation does not allow assigning them to a certain individual module. For more details please refer to LLD K15 Extended Configuration.

- External memory comprising RAM (XRAM), ROM including the routines for the chip management (RMS), test ROM containing the test routines (STS) and the Non Volatile Memory (EEPROM) with error detection (EDC) and error correction (ECC). Please refer to Table 3 for the memory sizes by derivate.

- True random number generator (RNG)

- Checksum module (CRC)

- Interrupt module (INT)

- Input Logic (INP)

- Timer (TIM)

- Address and data bus (ADBUS)

- SFR bus (SBUS)

- Memory bus (MBUS)

- DES accelerator (DDC), used for fast calculations of the DES algorithm.

- Extended configuration (CFG\_EXT), extended SFR registers for general purposes and chip configuration

- The Advanced Cryptographic Engine ACE has been implemented in order to use the same masks as for the SLE66CX162PE and SLE66CX80PE. Nevertheless the ACE is blocked and can not be used.

#### 2.2.2 Firmware and software of the TOE

The entire firmware of the IC consists of two different parts. The one is the RMS routines for EEPROM programming, security functions test, and random number online testing (Resource Management System, IC Dedicated Support Software in Smartcard IC Platform Protection Profile). The RMS routines are stored from Infineon Technologies AG in a reserved area of the normal user ROM. The other is the STS consisting of test and initialization routines (Self Test Software, IC Dedicated Test Software in Smartcard IC Platform Protection Profile). The especially protected test ROM and are not accessible for the user software.

The above definitions of the TOE result in the interfaces described below.

#### 2.2.2.1 Interfaces of the TOE

- The physical interface of the TOE to the external environment is the entire surface of the IC.

- The electrical interface of the TOE to the external environment is:

- The data-oriented I/O interface to the TOE is formed by the I/O pad.

- The interface to the firmware is constituted by special registers used for hardware configuration and control (Special Function Registers, SFR).

- The interface of the TOE to the operating system is constituted on the one hand by the RMS routine calls and on the other by the instruction set of the TOE.

- The interface of the TOE to the test routines is formed by the STS test routine call, i.e. entry to test mode (STS-TM entry).

#### 2.2.3 Guidance documentation

The guidance documentation consists of the [Databook] (and additional errata sheets) which contains the description of all interfaces of the software to the hardware relevant for programming the TOE.

In addition programming examples for more specific topics like secure use of cryptography are documented in form of application notes. The application notes are part of the development kit provided to the software developer. The monthly updated list of application notes is provided from Infineon Technologies AG [Status].

Finally the certification report will contain an overview of the recommendations to the software developer regarding the secure use of the TOE. These recommendations are also included in the ordinary documentation.

The list of guidance documentation is given in Annex 9.1.

#### 2.2.4 Forms of delivery

The TOE can be delivered in form of complete modules or in form of plain wafers. The delivery can therefore be at the end of phase 3 or at the end of phase 4 according to Smartcard IC Platform Protection Profile. Nevertheless in both cases the TOE is finished and the extended test features are removed. In this document are always both cases mentioned to avoid incorrectness but from the security policy point of view the two cases are identical.

The delivery to the software developer (phase 2 -> phase 1) contains the development package and is delivered in form of documentation as described above, data carriers containing the tools and emulators as development and debugging tool.

#### 2.2.5 Production sites

The TOE may be produced in the production site listed below (listed in Table 4). The chip layout is not changed in this case and also the production testing does not differ. To distinguish the different production sites the chip identification number is coded as shown in Table 4. The exact coding of the chip identification data is described in [Databook] section 7.3.5.1.

| Production Site | Sales name  | Internal name | Design status | Chip Identification                              |

|-----------------|-------------|---------------|---------------|--------------------------------------------------|

|                 |             |               |               | (upper nibble of address<br>08000AH, hex format) |

| Dresden         | SLE66C166PE | m1531         | A24           | 95H                                              |

Table 4: Production site in chip identification

# **3 TOE Security Environment**

For this chapter the Smartcard IC Platform Protection Profile can be applied completely. A summary is given in the following.

#### 3.1 Definition of Assets

The primary assets concern the User Data which includes the data as well as program code (Smartcard Embedded Software). This asset has to be protected while being executed and on the other hand when the TOE is not in operation. This leads to the three primary assets

- User Data

- Smartcard Embedded Software

- TOE's correct operation

The specific functions of the TOE introduce additional assets.

• the random numbers generated by the TOE

The class of secondary assets consists of the following.

- logical design data,

- physical design data,

- IC Dedicated Software, Initialisation Data and Pre-personalisation Data, TSF data

- specific development aids,

- test and characterisation related data,

- material for software development support, and

- photo masks and products in any form

For details see Smartcard IC Platform Protection Profile section 3.1.

#### 3.2 Assumptions

The assumptions defined in the Smartcard IC Platform Protection Profile concern the phases where the TOE has left the chip manufacturer.

| A.Process-Card | Protection during Packaging, Finishing and Personalisation |

|----------------|------------------------------------------------------------|

| A.Plat-Appl    | Usage of Hardware Platform                                 |

| A.Resp-Appl    | Treatment of User Data                                     |

The support of cipher schemas needs to make an additional assumption.

| V1.0 | Date: 2005-08-16 | Page: 11/46 |

|------|------------------|-------------|

The developer of the Smartcard Embedded Software must ensure the appropriate "Usage of Keydependent Functions (A.Key-Function)" while developing this software in Phase 1 as specified below.

A.Key-Function Usage of Key-dependent Functions

Key-dependent functions (if any) shall be implemented in the Smartcard Embedded Software in a way that they are not susceptible to leakage attacks (as described under T.Leak-Inherent and T.Leak-Forced).

Note that here the routines which may compromise keys when being executed are part of the Smartcard Embedded Software. In contrast to this the threats T.Leak-Inherent and T.Leak-Forced address (i) the cryptographic routines which are part of the TOE and (ii) the processing of User Data including cryptographic keys.

For details see Smartcard IC Platform Protection Profile section 3.2.

#### 3.3 Threats

The threats are directed against the assets. The threat is a general description of "What one wants to do" and might contain several specific attacks ("How one wants to do it"). The more detailed description of specific attacks is given later on in the process of evaluation and certification. An overview on attacks is given in Smartcard IC Platform Protection Profile.

| T.Phys-Manipulation | Physical Manipulation                   |

|---------------------|-----------------------------------------|

| T.Phys-Probing      | Physical Probing                        |

| T.Malfunction       | Malfunction due to Environmental Stress |

| T.Leak-Inherent     | Inherent Information Leakage            |

| T.Leak-Forced       | Forced Information Leakage              |

| T.Abuse-Func        | Abuse of Functionality                  |

| T.RND               | Deficiency of Random Numbers            |

Table 5: Threats to Smartcards according to the Protection Profile

For details see Smartcard IC Platform Protection Profile section 3.2.

#### 3.4 Organisational Security Policies

The TOE has to be protected during the first phases of their lifecycle (phases 2 up to TOE delivery)<sup>2</sup>. Later on each variant of the TOE has to protect itself. The organisational security policy covers this aspect.

P.Process-TOE Protection during TOE Development and Production

$<sup>^{2}</sup>$  The TOE can be delivered either after phase 3 or after phase 4.

| V1.0 Date: 2005-08-16 Page: 12/46 |

|-----------------------------------|

|-----------------------------------|

Infineon

See Smartcard IC Platform Protection Profile for a detailed description.

Due to the augmentations of the Smartcard IC Platform Protection Profile an additional policy is introduced.

#### 3.4.1 Augmented organisational security policy

The TOE provides specific security functionality which can be used by the Smartcard Embedded Software. In the following specific security functionality is listed which is not derived from threats identified for the TOE's environment because it can only be decided in the context of the smartcard application, against which threats the Smartcard Embedded Software will use the specific security functionality.

The IC Developer / Manufacturer must apply the policy "Additional Specific Security Functionality (P.Add-Functions)" as specified below.

P.Add-Functions Additional Specific Security Functionality

The TOE shall provide the following specific security functionality to the Smartcard Embedded Software:

- Area based Memory Access Control

- Triple Data Encryption Standard (3DES)

|  | V1.0 | Date: 2005-08-16 | Page: 13/46 |

|--|------|------------------|-------------|

|--|------|------------------|-------------|

# 4 Security objectives

For this chapter the Smartcard IC Platform Protection Profile can be applied completely. Only a short overview is given in the following.

### 4.1 Security objectives for the TOE

See Smartcard IC Platform Protection Profile.

Table 6: Objectives for Smartcards according to the Protection Profile

| O.Phys-Manipulation | Protection against Physical Manipulation                      |

|---------------------|---------------------------------------------------------------|

| O.Phys-Probing      | Protection against Physical Probing                           |

| O.Malfunction       | Protection against Malfunction due to<br>Environmental Stress |

| O.Leak-Inherent     | Protection against Inherent Information Leakage               |

| O.Leak-Forced       | Protection against Forced Information Leakage                 |

| O.Abuse-Func        | Protection against Abuse of Functionality                     |

| O.Identification    | TOE Identification                                            |

| O.RND               | Random Numbers                                                |

The TOE shall provide "Additional Specific Security Functionality (O.Add-Functions)" as specified below.

O.Add-Functions Additional Specific Security Functionality

The TOE must provide the following specific security functionality to the Smartcard Embedded Software:

- Area based Memory Access Control

- Triple Data Encryption Standard (3DES)

Table 7: Additional objectives due to TOE specific functions and augmentations

| O.Add-Functions | Additional specific security functionality |

|-----------------|--------------------------------------------|

|-----------------|--------------------------------------------|

#### 4.2 Security objectives for the environment

The detailed description of the environmental security objectives is given in the Smartcard IC Platform Protection Profile. The list of objectives is in Table 8.

| Phase 1 | OE.Plat-Appl | Usa | ge of Ha | rdware Platform | 1      |      |       |

|---------|--------------|-----|----------|-----------------|--------|------|-------|

|         |              |     |          |                 |        |      |       |

|         |              |     | V1.0     | Date: 2005-08   | 3-16 P | ade: | 14/46 |

|                                         | OE.Resp-Appl    | Treatment of User Data                                     |

|-----------------------------------------|-----------------|------------------------------------------------------------|

| Phase 2 up to<br>TOE delivery           | OE.Process-TOE  | Protection during TOE Development and Production           |

| TOE delivery<br>up to end of<br>phase 6 | OE.Process-Card | Protection during Packaging, Finishing and Personalisation |

#### 4.2.1 Clarification of "Usage of Hardware Platform (OE.Plat-Appl)"

Regarding the cryptographic services this objective of the environment has to be clarified. The TOE supports DES algorithm schemes as additional specific security functionality. If required the Smartcard Embedded Software shall use these cryptographic services of the TOE and their interface as specified. When key-dependent functions implemented in the Smartcard Embedded Software are just being executed, the Smartcard Embedded Software must provide protection against disclosure of confidential data (User Data) stored and/or processed in the TOE by using the methods described under "Inherent Information Leakage (T.Leak-Inherent)" and "Forced Information Leakage (T.Leak-Forced)".

Regarding the area based access control this objective of the environment has to be clarified. For the separation of different applications the Smartcard Embedded Software (Operating System) may implement a memory management scheme based upon security mechanisms of the TOE.

#### 4.2.2 Clarification of "Treatment of User Data (OE.Resp-Appl)"

Regarding the cryptographic services this objective of the environment has to be clarified. By definition cipher or plain text data and cryptographic keys are User Data. The Smartcard Embedded Software shall treat these data appropriately, use only proper secret keys (chosen from a large key space) as input for the cryptographic function of the TOE and use keys and functions appropriately in order to ensure the strength of cryptographic operation.

This means that keys are treated as confidential as soon as they are generated. The keys must be unique with a very high probability, as well as cryptographically strong. If keys are imported into the TOE and/or derived from other keys, quality and confidentiality must be maintained. This implies that appropriate key management has to be realised in the environment.

Regarding the area based access control this objective of the environment has to be clarified. The treatment of User Data is also required when a multi-application operating system is implemented as part of the Smartcard Embedded Software on the TOE. In this case the multi-application operating system should not disclose security relevant user data of one application to another application when it is processed or stored on the TOE.

|  | V | '1.0 Date | e: 2005-08-16 | Page: | 15/46 | I |

|--|---|-----------|---------------|-------|-------|---|

|--|---|-----------|---------------|-------|-------|---|

# 5 IT security requirements

For this chapter the Smartcard IC Platform Protection Profile can be applied completely.

#### 5.1 TOE security requirements

See Smartcard IC Platform Protection Profile.

The following tables provide an overview of the used functional security requirements. Requirements which are not drawn from CC Part 2 are marked in italics.

Table 9: Security functional requirements defined in Smartcard IC Platform Protection Profile

|           | Security Functional Requirement               | Refined in [PP] |

|-----------|-----------------------------------------------|-----------------|

| FRU_FLT.2 | "Limited fault tolerance"                     | Yes             |

| FPT_FLS.1 | "Failure with preservation of secure state"   | Yes             |

| FPT_SEP.1 | "TSF domain separation"                       | Yes             |

| FMT_LIM.1 | "Limited capabilities"                        |                 |

| FMT_LIM.2 | "Limited availability"                        |                 |

| FAU_SAS.1 | "Audit storage"                               |                 |

| FPT_PHP.3 | "Resistance to physical attack"               | Yes             |

| FDP_ITT.1 | "Basic internal transfer protection"          | Yes             |

| FDP_IFC.1 | "Subset information flow control"             |                 |

| FPT_ITT.1 | "Basic internal TSF data transfer protection" | Yes             |

| FCS_RND.1 | "Quality metric for random numbers"           |                 |

Table 10: Augmented security functional requirements

| Security Functional Requirement                         |

|---------------------------------------------------------|

| FPT_TST.2 "Subset TOE security testing"                 |

| FDP_ACC.1 "Subset access control"                       |

| FDP_ACF.1 "Security attribute based access control"     |

| FMT_MSA.3 "Static attribute initialisation"             |

| FMT_MSA.1 "Management of security attributes"           |

| FMT_SMF.1 "Specification of Management functions"       |

| FCS_COP.1 "Cryptographic support"                       |

| FDP_SDI.1 "Stored data integrity monitoring"            |

| FDP_SDI.2 "Stored data integrity monitoring and action" |

#### 5.1.1 TOE security functional requirements

The detailed description of the security functional requirements is given in the Smartcard IC Platform Protection Profile. These security functional requirements are listed in Table 9. In the last

|  |  | V1.0 | Date: 2005-08-16 | Page: 16/46 |

|--|--|------|------------------|-------------|

|--|--|------|------------------|-------------|

column it is marked if the requirement is refined in the [PP]. The refinements are also valid for this ST. The additional security functional requirements are listed in Table 10. The necessary assignments are done in section 7.2. The description of the additional security functional requirements is given in the following.

#### 5.1.1.1 Subset TOE security testing (FPT\_TST.2)

The security is strongly dependent on the correct operation of the security functions. Therefore, the TOE shall support that particular security functions or mechanisms are tested in the operational phase (Phase 7). The tests can be initiated by the Smartcard Embedded Software and/or by the TOE.

Part 2 of the Common Criteria provides the security functional component "TSF testing (FPT\_TST.1)". The component FPT\_TST.1 provides the ability to test the TSF's correct operation.

For the user it is important to know which security functions or mechanisms can be tested. The functional component FPT\_TST.1 does not mandate to explicitly specify the security functions being tested. In addition, FPT\_TST.1 requires verification of the integrity of TSF data and of the stored TSF executable code which might violate the security policy. Therefore, the security functional component **Subset TOE security testing (FPT\_TST.2)** has been newly created. This component allows that particular parts of the security mechanisms and functions provided by the TOE are tested.

#### FPT\_TST.2

The security functional component Subset TOE security testing (FPT\_TST.2) has been newly created (Common Criteria Part 2 extended). This component allows that particular parts of the security mechanisms and functions provided by the TOE can be tested after TOE Delivery. This security functional component is used instead of the functional component FPT\_TST.1 from Common Criteria Part 2. For the user it is important to know which security functions or mechanisms can be tested. The functional component FPT\_TST.1 does not mandate to explicitly specify the security functions being tested. In addition, FPT\_TST.1 requires verifying the integrity of TSF data and stored TSF executable code which might violate the security policy.

The TOE shall meet the requirement "Subset TOE testing (FPT\_TST.2)" as specified below (Common Criteria Part 2 extended).

- **FPT\_TST.2** Subset TOE testing

- Hierarchical to: No other components.

- FPT\_TST.2.1 The TSF shall run a suite of self tests<sup>3</sup> at the request of the authorised user<sup>4</sup> to demonstrate the correct operation of the environmental sensor mechanisms:

<sup>&</sup>lt;sup>4</sup> The term "authorized user" refers to the Smartcard Embedded Software running on the TOE

|  |  | V1.0 | Date: 2005-08-16 | Page: | 17/46 |

|--|--|------|------------------|-------|-------|

|--|--|------|------------------|-------|-------|

<sup>&</sup>lt;sup>3</sup> The definition of the user mode self test function (Umslc) can be found in [Databook] chapter 6, labeled as SIeSIcTest

Frequency Monitoring, Voltage Sensor, Light Detection, Temperature Sensor, the RNG with help of the live test the active shield. Dependencies: FPT\_AMT.1 Abstract machine testing

Public

5.1.1.2 Memory access control

Usage of multiple applications in one Smartcard often requires code and data separation in order to prevent that one application can access code and/or data of another application. For this reason the TOE provides Area based Memory Access Control. The underlying memory management unit (MMU) is documented in section 5 of the [DataBook].

The security service being provided is described in the Security Function Policy (SFP) **Memory Access Control Policy**. The security functional requirement **"Subset access control (FDP\_ACC.1)**" requires that this policy is in place and defines the scope were it applies. The security functional requirement **"Security attribute based access control (FDP\_ACF.1)**" defines addresses security attribute usage and characteristics of policies. It describes the rules for the function that implements the Security Function Policy (SFP) as identified in FDP\_ACC.1. The decision whether an access is permitted or not is taken based upon attributes allocated to the software. The Smartcard Embedded Software defines the attributes and memory areas. The corresponding permission control information is evaluated "on-the-fly" by the hardware so that access is granted/effective or denied/inoperable.

The security functional requirement "Static attribute initialisation (FMT\_MSA.3)" ensures that the default values of security attributes are appropriately either permissive or restrictive in nature. Alternative values can be specified by any subject provided that the Memory Access Control Policy allows that. This is described by the security functional requirement "Management of security attributes (FMT\_MSA.1)". The attributes are determined during TOE manufacturing (FMT\_MSA.3) or set at run-time (FMT\_MSA.1).

From TOE's point of view the different roles in the Smartcard Embedded Software can be distinguished according to the memory based access control. However the definition of the roles belongs to the user software.

The following Security Function Policy (SFP) **Memory Access Control Policy** is defined for the requirement "Security attribute based access control (FDP\_ACF.1)":

#### Memory Access Control Policy

The TOE shall control read, write, delete, execute accesses of software running at two different modes (system mode active during interrupt execution or application mode active during other executing) on data and code stored in memory areas.

The TOE shall restrict the ability to define, to change or at least to finally accept the applied rules (as mentioned in FDP\_ACF.1) to software running at interrupt level (in the system mode).

The TOE shall meet the requirement "Subset access control (FDP\_ACC.1)" as specified below.

FDP\_ACC.1 Subset access control

|  |  | V1.0 | Date: 2005-08-16 | Page: 18/46 |  |

|--|--|------|------------------|-------------|--|

|--|--|------|------------------|-------------|--|

| Hierarchical to: | No other components.                                                                                                                                                                                                                                                                                                               |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FDP_ACC.1.1      | The TSF shall enforce the Memory Access Control Policy on all<br>subjects (software running at system mode active during interrupt<br>execution or application mode active during other executing), all<br>objects (data including code stored in memories) and all the<br>operations defined in the Memory Access Control Policy. |

| Dependencies:    | FDP_ACF.1 Security attribute based access control                                                                                                                                                                                                                                                                                  |

The TOE shall meet the requirement "Security attribute based access control (FDP\_ACF.1)" as specified below.

- FDP\_ACF.1Security attribute based access control

- Hierarchical to: No other components.

- FDP\_ACF.1.1<sup>5</sup> The TSF shall enforce the *Memory Access Control Policy* to objects based on the following: *Subject*:

- software running at system mode active during interrupt execution or application mode active during other executing attributes:

- the interrupt execution level where the software is executed (interrupt / non-interrupt) and/or

- Object:

- data including code stored in memories attributes:

- the memory area where the access is performed to and/or

- the operation to be performed.

- FDP\_ACF.1.2 The TSF shall enforce the following rules to determine if an operation among controlled subjects and controlled objects is allowed: *evaluate the corresponding permission control information before the access so that accesses to be denied can not be utilised by the subject attempting to perform the operation.*

- FDP\_ACF.1.3 The TSF shall explicitly authorise access of subjects to objects based on the following additional rules: *none*.

- FDP\_ACF.1.4 The TSF shall explicitly deny access of subjects to objects based on the *following additional rules: none*.

- Dependencies: FDP\_ACC.1 Subset access control

FMT\_MSA.3 Static attribute initialisation

The TOE shall meet the requirement "Static attribute initialisation (FMT\_MSA.3)" as specified below.

**FMT\_MSA.3** Static attribute initialisation

FDP\_ACF.1.1 The TSF shall enforce the [assignment: access control SFP] to objects based on the following: [assignment: list of subjects and objects controlled under the indicated SFP, and. for each, the SFP-relevant security attributes, or named groups of SFP-relevant security attributes].

<sup>&</sup>lt;sup>5</sup> The following element is changed as a result of Interpretation 103.

| Linfineon        | Public SLE66C166PE Security Target                                                                                                                                                                                    |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Hierarchical to: | No other components.                                                                                                                                                                                                  |  |

| FMT_MSA.3.1      | The TSF shall enforce the <i>Memory Access Control Policy</i> to provide <i>well defined</i> <sup>6</sup> default values for security attributes that are used to enforce the SFP.                                    |  |

| FMT_MSA.3.2      | The TSF shall allow any subject (provided that the Memory Access Control Policy is enforced and the necessary access is therefore allowed) <sup>7</sup> to specify alternative initial values to override the default |  |

values when an object or information is created.

Dependencies: FMT\_MSA.1 Management of security attributes

FMT\_SMR.1 Security roles

The TOE shall meet the requirement "Management of security attributes (FMT\_MSA.1)" as specified below:

| FMT_MSA.1 | Management of security attributes |

|-----------|-----------------------------------|

|-----------|-----------------------------------|

Hierarchical to: No other components.

- FMT\_MSA.1.1 The TSF shall enforce the *Memory Access Control Policy* to restrict the ability to *change default, modify or delete* the security attributes *permission control information* to *running at interrupt level (system mode).*

- Dependencies: [FDP\_ACC.1 Subset access control or

FDP\_IFC.1 Subset information flow control]

FMT\_SMF.1 Specification of management functions

FMT\_SMR.1 Security roles

The TOE shall meet the requirement "Specification of management functions (FMT\_SMF.1)" as specified below:

| FMT_SMF.1        | Specification of management functions                                                                                              |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Hierarchical to: | No other components                                                                                                                |

| FMT_SMF.1.1      | The TSF shall be capable of performing the following security management functions: access the configuration registers of the MMU. |

| Dependencies:    | No dependencies                                                                                                                    |

#### 5.1.1.3 Support of cipher schemas

FCS\_COP.1 Cryptographic operation requires a cryptographic operation to be performed in accordance with a specified algorithm and with a cryptographic key of specified sizes. The

<sup>&</sup>lt;sup>7</sup> The Smartcard Embedded Software is intended to set the memory access control policy

|--|

<sup>&</sup>lt;sup>6</sup> The static definition of the access rules is documented in [DataBook] section 5

specified algorithm and cryptographic key sizes can be based on an assigned standard; dependencies are discussed in Section 8.2.

The following additional specific security functionality is implemented in the TOE:

- Triple Data Encryption Standard (3DES)

#### **Triple-DES Operation**

The DES Operation of the TOE shall meet the requirement "Cryptographic operation (FCS\_COP.1)" as specified below.

| FCS_COP.1        | Cryptographic operation                                                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hierarchical to: | No other components.                                                                                                                                                                                                                          |

| FCS_COP.1.1      | The TSF shall perform <i>encryption and decryption</i> in accordance with a specified cryptographic algorithm <i>Triple Data Encryption Standard</i> (3DES) and cryptographic key sizes of 112 bit that meet the following <i>standards</i> : |

|                  | U.S. Department of Commerce / National Bureau of Standards<br>Data Encryption Standard (DES), FIPS PUB 46-3, 1999 October 25,<br>keying option 2                                                                                              |

| Dependencies:    | [FDP_ITC.1 Import of user data without security attributes, or                                                                                                                                                                                |

|                  | FDP_ITC.2 Import of user data with security attributes, or                                                                                                                                                                                    |

|                  | FCS_CKM.1 Cryptographic key generation]                                                                                                                                                                                                       |

|                  | FCS_CKM.4 Cryptographic key destruction                                                                                                                                                                                                       |

|                  | FMT_MSA.2 Secure security attributes                                                                                                                                                                                                          |

#### 5.1.1.4 Data Integrity

#### CRC-Checksum

The TOE shall meet the requirement "Stored data integrity monitoring (FDP\_SDI.1)" as specified below:

- FDP\_SDI.1Stored data integrity monitoring

- Hierarchical to: No other components

- FDP\_SDI.1.1 The TSF shall monitor user data stored within the TSC for inconsistencies between stored data and corresponding CRC checksum on all objects, based on the following attributes: CRC checksum value.

Dependencies: No dependencies

#### Error Detection Code and Error Correction Code (EDC, ECC)

The TOE shall meet the requirement "Stored data integrity monitoring (FDP\_SDI.1)" as specified below:

| FDP_SDI.2 | Stored data integrity | monitoring and action |

|-----------|-----------------------|-----------------------|

|           |                       |                       |

Hierarchical to: FDP\_SDI.1

| V1.0 Date: 2005-08-16 | Page: | 21/46 |

|-----------------------|-------|-------|

|-----------------------|-------|-------|

| Cinfineon     | Public                                                                                                                                          | SLE66C166PE<br>Security Target |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| FDP_SDI.2.1   | The TSF shall monitor user data stored w<br>inconsistencies between stored data and c<br>checksum on all objects, based on the follow<br>value. | corresponding ECC              |

| FDP_SDI.2.2   | Upon detection of a data integrity error, the TSI errors and inform the user about more bit errors.                                             | shall: correct 1 bit           |

| Dependencies: | No dependencies                                                                                                                                 |                                |

#### 5.1.2 TOE security assurance requirements

The evaluation assurance level is EAL 5 augmented. Table 11 describes the security assurance requirements. The increase of the assurance components compared to the Smartcard IC Platform Protection Profile is expressed with bold letters. The augmentation of the assurance components to level EAL5 is given in italic letters.

| Aspect        | Acronym   | Description                                       | Refinement |

|---------------|-----------|---------------------------------------------------|------------|

| Configuration | ACM_AUT.1 | Partial CM automation                             |            |

| management    | ACM_CAP.4 | Generation support and acceptance procedures      | in PP      |

|               | ACM_SCP.3 | Development tools CM coverage                     | in ST      |

| Delivery and  | ADO_DEL.2 | Detection of modification                         | in PP      |

| operation     | ADO_IGS.1 | Installation, generation, and start-up procedures | in PP      |

| Development   | ADV_FSP.3 | Semiformal functional specification               | in ST      |

|               | ADV_HLD.3 | Semiformal high-level design                      |            |

|               | ADV_IMP.2 | Implementation of the TSF                         |            |

|               | ADV_INT.1 | Modularity                                        |            |

|               | ADV_LLD.1 | Descriptive low-level design                      |            |

|               | ADV_RCR.2 | Semiformal correspondence demonstration           |            |

|               | ADV_SPM.3 | Formal TOE security policy model                  |            |

| Guidance      | AGD_ADM.1 | Administrator guidance                            | in PP      |

| documents     | AGD_USR.1 | User guidance                                     | in PP      |

| Life cycle    | ALC_DVS.2 | Sufficiency of security measures                  | in PP      |

| support       | ALC_LCD.2 | Standardised life-cycle model                     |            |

|               | ALC_TAT.2 | Compliance with implementation standards          |            |

| Tests         | ATE_COV.2 | Analysis of coverage                              | in PP      |

|               | ATE_DPT.2 | Testing: low-level design                         |            |

| Aspect        | Acronym   | Description                                  | Refinement |

|---------------|-----------|----------------------------------------------|------------|

|               | ATE_FUN.1 | Functional testing                           |            |

|               | ATE_IND.2 | Independent testing – sample                 |            |

| Vulnerability | AVA_CCA.1 | Covert channel analysis                      |            |

| assessment    | AVA_MSU.3 | Validation of analysis                       |            |

|               | AVA_SOF.1 | Strength of TOE security function evaluation |            |

|               | AVA_VLA.4 | Highly resistant                             |            |

#### 5.1.3 Refinements

Some refinements are taken unchanged from the Smartcard IC Platform Protection Profile. In some cases a clarification is necessary. In Table 11 an overview is given where the refinement is done. Two refinements from the Smartcard IC Platform Protection Profile have to be discussed here in the Security Target, as the assurance level is increased.

#### 5.1.3.1 Configuration Management Scope (ACM\_SCP)

The refinement from the Smartcard IC Platform Protection Profile can be applied even at the chosen assurance level EAL 5 augmented with ACM\_SCP.3. The assurance package ACM\_SCP.2 is extended to ACM\_SCP.3 with aspects regarding the development tools. The refinement is not touched.

#### Refinement for CM scope (ACM\_SCP)

The "TOE implementation representation" within the scope of the CM shall include at least:

- logical design data,

- physical design data,

- IC Dedicated Software,

- Smartcard Embedded Software,

- final physical design data necessary to produce the photomasks, and

- photomasks.

#### 5.1.3.2 Functional Specification (ADV\_FSP)

The refinement from the Smartcard IC Platform Protection Profile can be applied even at the chosen assurance level EAL 5 augmented with ADV\_FSP.3. The assurance package ADV\_FSP.2 is extended to ADV\_FSP.3 with aspects regarding the descriptive level. The level is increased from informal to semi formal with informal description. Refinements are not touched from this measure.

For details of the refinement see Smartcard IC Platform Protection Profile.

|--|

#### 5.2 Security requirements for the Environment

#### 5.2.1 Security requirements for the IT Environment

#### 5.2.1.1 Security requirements for the IT Environment resulting from FCS\_COP.1

The security functional requirement "Cryptographic operation (FCS\_COP.1)" met by TOE has the following dependencies

- [FDP\_ITC.1 Import of user data without security attributes or FDP\_ITC.2 Import of user data with security attributes or FCS\_CKM.1 Cryptographic key generation],

- FCS\_CKM.4 Cryptographic key destruction,

- FMT\_MSA.2 Secure security attributes.

These requirements all address the appropriate management of cryptographic keys used by the specified cryptographic function and are not part of the Smartcard IC Platform Protection Profile. Most requirements concerning key management shall be fulfilled by the environment since the Smartcard Embedded Software is designed for a specific application context and uses the cryptographic functions provided by the TOE.

In the following the dependencies are discussed for the 3DES algorithm.

#### 5.2.1.2 3DES

The environment shall meet the requirement "Import of user data without security attributes FDP\_ITC.1)" as specified below.

FDP\_ITC.1 Import of user data without security attributes

Hierarchical to: No other components.

- FDP\_ITC.1.1 The TSF shall enforce the Access Control Policy or Information Flow Control Policy when importing user data, controlled under the SFP, from outside of the TSC.

- FDP\_ITC.1.2 The TSF shall ignore any security attributes associated with the user data when imported from outside the TSC.

- FDP\_ITC.1.3 The TSF shall enforce the following rules when importing user data controlled under the SFP from outside the TSC: Data Access Control Policy or Information Flow Control Policy.

- Dependencies: [FDP\_ACC.1 Subset access control, or FDP\_IFC.1 Subset information flow control]

FMT\_MSA.3 Static attribute initialisation

or

The environment shall meet the requirement "Import of user data with security attributes FDP\_ITC.2)" as specified below.

FDP\_ITC.2 Import of user data without security attributes

Hierarchical to: No other components.

- FDP\_ITC.2.1 The TSF shall enforce the Access Control Policies or Information Flow Control Policies when importing user data, controlled under the SFP, from outside of the TSC.

- FDP\_ITC.2.2 The TSF shall ensure that the protocol used provides for the unambiguous association between the security attributes and the user data received.

|--|

|               | Public SLE66C166PE Security Target                                                                                                                                          |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FDP_ITC.2.3   | The TSF shall ensure that interpretation of the security attributes of the imported user data is as intended by the source of the user data.                                |

| FDP_ITC.2.4   | The TSF shall use the security attributes associated with the imported user data.                                                                                           |

| FDP_ITC.2.5   | The TSF shall enforce the following rules when importing user data controlled under the SFP from outside the TSC: Access Control Policy or Information Flow Control Policy. |

| Dependencies: | [FDP_ACC.1 Subset access control, or FDP_IFC.1 Subset information flow control]                                                                                             |

|               | [FTP_ITC.1 Inter-TSF trusted channel, or FTP_TRP.1 Trusted path]                                                                                                            |

|               | FPT_TDC.1 Inter-TSF basic TSF data consistency                                                                                                                              |

or

The environment shall meet the requirement "Cryptographic key generation (FCS\_CKM.1)" as specified below.

FCS\_CKM.1 Cryptographic key generation (3DES)

Hierarchical to: No other components.

- FCS\_CKM.1.1 The TSF shall generate cryptographic keys in accordance with a specified cryptographic key generation algorithm *3DES* and specified cryptographic key sizes *112 bit* that meet the following: *U.S. Department of Commerce / National Bureau of Standards Data Encryption Standard (DES), FIPS PUB 46-3, 1999 October 25, keying option 2.*

- Dependencies: [FCS\_CKM.2 Cryptographic key distribution or FCS\_COP.1 Cryptographic operation]

FCS\_CKM.4 Cryptographic key destruction

FMT\_MSA.2 Secure security attributes

Remark: Cryptographic keys for the 3DES algorithm have to be generated in the environment and imported into the TOE.

The environment shall meet the requirement "Cryptographic key destruction (FCS\_CKM.4)" as specified below.

FCS\_CKM.4 Cryptographic key destruction

Hierarchical to: No other components.

- FCS\_CKM.4.1 The TSF shall destroy cryptographic keys in accordance with a specified cryptographic key destruction method *change key and change key with certificate verification that* meets the following: ISO/IEC 7816.

- Dependencies: [FDP\_ITC.1 Import of user data without security attributes or FDP\_ITC.2 Import of user data with security attributes or FCS\_CKM.1 Cryptographic key generation]

FMT\_MSA.2 Secure security attributes

The environment shall meet the requirement "Secure security attributes (FMT\_MSA.2)" as specified below.

FMT\_MSA.2 Secure security attributes

Hierarchical to: No other components.

| FMT_MSA.2.1   | The TSF shall ensure that only secure values are accepted for security attributes. |

|---------------|------------------------------------------------------------------------------------|

| Dependencies: | ADV_SPM.1 Informal TOE security policy model                                       |

|               | [FDP_ACC.1 Subset access control or FDP_IFC.1 Subset information flow control]     |

|               | FMT_MSA.1 Management of security attributes                                        |

|               | FMT_SMR.1 Security roles                                                           |

#### 5.2.2 Security Requirements for the Non-IT-Environment

In the following security requirements for the Non-IT-Environment are defined. For the development of the Smartcard Embedded Software (in Phase 1) the requirement RE.Phase-1 is valid.

RE.Phase-1 Design and Implementation of the Smartcard Embedded Software

The developers shall design and implement the Smartcard Embedded Software in such way that it meets the requirements from the following documents: (i) hardware data sheet for the TOE, (ii) TOE application notes, and (iii) findings of the TOE evaluation reports relevant for the Smartcard Embedded Software.

The developers shall implement the Smartcard Embedded Software in a way that it protects security relevant User Data (especially cryptographic keys) as required by the security needs of the specific application context.

The responsible parties for the Phases 4-6 are required to support the security of the TOE by appropriate measures:

RE.Process-Card Protection during Packaging, Finishing and Personalisation

The Card Manufacturer (after TOE Delivery up to the end of Phase 6) shall use adequate security measures to maintain confidentiality and integrity of the TOE and of its manufacturing and test data (to prevent any possible copy, modification, retention, theft or unauthorised use).

The Smartcard Embedded Software shall meet the requirements "Cipher Schemas (RE.Cipher)" as specified below.

RE.Cipher Cipher Schemas

The developers of Smartcard Embedded Software must not implement routines in a way which may compromise keys when the routines are executed as part of the Smartcard Embedded Software. Performing functions which access cryptographic keys could allow an attacker to misuse these functions to gather information about the key which is used in the computation of the function.

Keys must be kept confidential as soon as they are generated. The keys must be unique with a very high probability, as well as

| V1.0 | Date: 2005-08-16 | Page: 26/46 |

|------|------------------|-------------|

|------|------------------|-------------|

cryptographically strong. For example, it must be ensured that it is not possible to derive the private key from a public key if asymmetric algorithms are used. If keys are imported into the TOE and/or derived from other keys, quality and confidentiality must be maintained. This implies that an appropriate key management has to be realised in the environment.

|  | V1.0 Date: 2005-08-16 P | Page: 27/46 |

|--|-------------------------|-------------|

|--|-------------------------|-------------|

# 6 TOE summary specification

The product overview is given in section 2.1. In the following the security functionality is described and the relation to the security functional requirements is shown.

The TOE is equipped with 9 security enforcing functions to meet the security functional requirements. The functions are:

SEF1: Operating state checking

SEF2: Phase management with test mode lock-out

SEF3: Protection against snooping

SEF4: Data encryption and data disguising

SEF5: Random number generation

SEF6: TSF self test

SEF7: Notification of physical attack

SEF8: Memory Management Unit (MMU)

SEF9: Cryptographic support

The following description of the security enforcing functions is a complete representation of the TSF.

#### 6.1 SEF1: Operating state checking

The correct function of the TOE is only given in the specified range of the environmental operating parameters. To prevent an attack exploiting those circumstances it is necessary to detect if the specified range is left.

All operating signals are filtered to prevent malfunction. The FRU\_FLT.2 "Limited fault tolerance" requirement is satisfied.

In addition the operating state is monitored with sensors for the operating voltage, clock signal frequency, and temperature and electro magnetic radiation. The TOE falls into the defined secure state in case of a specified range violation<sup>8</sup>. The defined secure state causes the chip internal reset process. The FPT\_FLS.1 "Failure with preservation of secure state"-requirement is satisfied.

The data in the EEPROM are automatically monitored by the EDC/ECC. In case of an error the memory content is either corrected by the ECC (1 bit errors). In case of one and more bit errors the user can select one of several options (NMI, MI, Reset or don't care). The IC therefore is protected by this mechanism against manipulation of memory content. The FDP\_SDI.2 "Stored data integrity monitoring and action" is satisfied.

In order to prevent accidental bit faults during production in the ROM, over the data stored in ROM a CRC-Checksum is calculated. The FDP\_SDI.1 "Stored data integrity monitoring" is satisfied.

The covered security functional requirements are FRU\_FLT.2, FPT\_FLS.1, FDP\_SDI.1, and FDP\_SDI.2. The SEF1 does not use probabilistic or permutational effects. Since the ROM CRC and the EDC/ECC functionality are not accessible via an external interface no direct attacks are possible. Therefore this function is not included in the SOF claim.

<sup>&</sup>lt;sup>8</sup> The operating state checking SEF1 can only work when the TOE is running and can not prevent reverse engineering.

#### 6.2 SEF2: Phase management with test mode lock-out