# **Security Target Lite**

## M7791 B12

Resistance to attackers with HIGH attack potential

## **Security Target Lite**

## Common Criteria v3.1 - EAL5+

## Security Target Introduction (ASE\_INT)

## **Table of Contents**

| Table of ( | Contents                                                            | 2  |

|------------|---------------------------------------------------------------------|----|

| 1          | Security Target Introduction (ASE_INT)                              | 4  |

| 1.1        | Security Target Lite and Target of Evaluation Reference             |    |

| 1.2        | TOE Overview                                                        |    |

| 1.2.1      | TOE Definition and Usage                                            | 5  |

| 1.2.2      | TOE major security features                                         |    |

| 2          | TOE Description                                                     | 7  |

| 2.1        | TOE Components                                                      |    |

| 2.1.1      | Hardware Components                                                 |    |

| 2.1.2      | Firmware and Software components                                    |    |

| 2.1.3      | User Guidance Components                                            |    |

| 2.2        | Physical Scope of the TOE                                           |    |

| 2.3        | Logical Scope of the TOE                                            |    |

| 2.4        | Interfaces of the TOE                                               |    |

| 2.5        | Forms of Delivery                                                   | 11 |

| 2.6        | Production sites                                                    | 12 |

| 2.7        | TOE Configuration                                                   | 12 |

| 2.7.1      | TOE initialization with Customer Software                           | 14 |

| 3          | Conformance Claims (ASE_CCL)                                        | 15 |

| 3.1        | CC Conformance Claim                                                |    |

| 3.2        | PP Claim                                                            |    |

| 3.3        | Package Claim                                                       |    |

| 3.4        | Conformance Rationale                                               |    |

| 3.4.1      | Security Problem Definition:                                        | 16 |

| 3.4.2      | Conformance Rationale:                                              | 16 |

| 3.4.3      | Adding Objective                                                    | 16 |

| 3.4.4      | Loader                                                              | 16 |

| 3.4.5      | Summary                                                             | 17 |

| 3.5        | Application Notes                                                   | 17 |

| 4          | Security Problem Definition (ASE_SPD)                               | 18 |

| 4.1        | Threats                                                             |    |

| 4.1.1      | Additional Threat due to TOE specific Functionality                 | 18 |

| 4.1.2      | Assets regarding the Threats                                        | 19 |

| 4.2        | Organizational Security Policies                                    |    |

| 4.3        | Assumptions                                                         | 19 |

| 5          | Security objectives (ASE_OBJ)                                       | 20 |

| 5.1        | Security objectives of the TOE                                      |    |

| 5.2        | Security Objectives for the development and operational Environment | 20 |

| 5.3        | Security Objectives Rationale                                       | 21 |

| 6          | Extended Component Definition (ASE_ECD)                             | 22 |

| 6.1        | Component "Subset TOE security testing (FPT_TST)"                   |    |

| 6.2        | Definition of FPT_TST.2                                             |    |

| 6.3        | TSF self test (FPT_TST)                                             | 23 |

| 7          | Security Requirements (ASE_REQ)                                     | 24 |

| 7.1        | TOE Security Functional Requirements                                |    |

| 7.1.1      | Definition required by [1]                                          |    |

| 7.1.2      | Extended Components FCS_RNG.1 and FAU_SAS.1                         |    |

| 7.1.2.1    | FCS_RNG                                                             |    |

| 7.1.2.2    | FAU_SAS                                                             |    |

| 7.1.3      | Subset of TOE testing                                               | 27 |

| 7.1.4      | Memory access control                                               | 27 |

## **Security Target Lite**

## Common Criteria v3.1 - EAL5+

## Security Target Introduction (ASE\_INT)

| 7.1.6    | Data Integrity                                                                 | 31 |

|----------|--------------------------------------------------------------------------------|----|

| 7.2      | Support of the Flash Loader                                                    | 32 |

| 7.3      | TOE Security Assurance Requirements                                            | 32 |

| 7.3.1    | Refinements                                                                    |    |

| 7.3.1.1  | Life cycle support (ALC_CMS)                                                   | 33 |

| 7.3.1.2  | Functional Specification (ADV_FSP)                                             | 33 |

| 7.4      | Security Requirements Rationale                                                | 34 |

| 7.4.1    | Rationale for the Security Functional Requirements                             | 34 |

| 7.4.1.1  | Dependencies of Security Functional Requirements                               | 35 |

| 7.4.2    | Rationale of the Assurance Requirements                                        | 35 |

| 8        | TOE Summary Specification (ASE_TSS)                                            | 37 |

| 8.1      | SF_DPM: Device Phase Management                                                | 37 |

| 8.2      | SF_PS: Protection against Snooping                                             | 37 |

| 8.3      | SF_PMA: Protection against Modifying Attacks                                   | 37 |

| 8.4      | SF_PLA: Protection against Logical Attacks                                     | 37 |

| 8.5      | SF_CS: Cryptographic Support                                                   |    |

| 8.6      | Assignment of Security Functional Requirements to TOE's Security Functionality |    |

| 8.7      | Security Requirements are internally Consistent                                | 39 |

| 9        | References                                                                     | 40 |

| 9.1      | Literature                                                                     | 40 |

| 10       | List of Abbreviations                                                          | 41 |

| 11       | Glossary                                                                       | 43 |

| Revision | History                                                                        | 45 |

|          |                                                                                |    |

Security Target Introduction (ASE\_INT)

## 1 Security Target Introduction (ASE\_INT)

### 1.1 Security Target Lite and Target of Evaluation Reference

The title of this document is Security Target Lite M7791 B12. The Security Target Lite comprises the Infineon Technologies SmartCard IC (Security Controller) M7791 B12 and with specific IC-dedicated firmware identifier V77.014.11.2 or V77.014.12.1.

The target of evaluation (TOE) M7791 B12 is described in the following sections. The Security Target Lite has the revision 1.3 and is dated 2021-10-27.

The Target of Evaluation (TOE) is an Infineon smartcard IC (Security Controller) M7791 B12 with specific IC-dedicated firmware. The versions are listed in Table 1.

The Security Target Lite is based on the Protection Profile "Smartcard IC Platform Protection Profile" [1].

The Protection Profile and the Security Target Lite are built in compliance to Common Criteria v3.1.

The ST takes into account all relevant current final interpretations.

The targeted certificate is EAL5+.

Security Target Introduction (ASE\_INT)

Table 1 Identification

|             | Version      | Date        | Registration                                                       |

|-------------|--------------|-------------|--------------------------------------------------------------------|

| Security    | this version | see cover   | M7791 B12                                                          |

| Target      |              | page        |                                                                    |

| Target of   | B12          |             | M7791 B12                                                          |

| Evaluation  |              |             |                                                                    |

|             |              |             | with Firmware consisting of STS, RMS, SAM, NRG software interface  |

|             |              |             | and FlashLoader; identifier V77.014.11.2 or V77.014.12.1           |

| Guidance    | v2.1         | 2019-09     | M7791 Hardware Reference Manual                                    |

| Documentati | v2.0         | 2020-02     | AMM Advanced Mode for NRG <sup>™</sup> SAM Addendum to M7791       |

| on          |              |             | Hardware Reference Manual Rev. 2.1, (optional)                     |

|             | 2015-04-01a  | 2015-04-01a | SLx 70 Family Production and Personalization User's Manual         |

|             | v9.14        | 2019-12-03  | SLE 70 Family Programmer's Reference User's Manual                 |

|             | 2021-07      | 2021-07     | M7791 Security Guidelines User's manual                            |

|             | v8.0         | 2019-12-17  | SLE77 Controller Family Solid Flash TM Controller for Security     |

|             |              |             | Applications - Errata Sheet                                        |

|             | 2014-11      | 2014-11     | Option 2 for Fast Startup                                          |

| Evaluation  | 1.0          | 13.01.2014  | Security IC Platform Protection Profile with Augmentation Packages |

| based on    |              |             | PP0084                                                             |

| Protection  |              |             |                                                                    |

| Profile     |              |             |                                                                    |

| Common      | Version 3.1  | 2017-April  | Common Criteria for Information Technology Security Evaluation     |

| Criteria    | Revision 5   |             | Part 1: Introduction and general model CCMB-2017-04-001            |

|             |              |             | Part 2: Security functional requirements CCMB-2017-04-002          |

|             |              |             | Part 3: Security Assurance Components CCMB-2017-04-003             |

A customer can identify the TOE and its configuration (for details see chapter 2.7) using a dedicated signalling sequence during startup in combination with firmware functions. The TOE answers this signaling sequence with a Generic Chip Identification Mode (GCIM). This GCIM outputs a.o. a chip identifier byte, design step, firmware identifier, metal configuration identifier, temperature range and system frequency. The identification data and configuration details are described in the M7791 Hardware Reference Manual.

The main difference between the two firmware versions is their timing behavior during startup. In case of FW ID V77.014.12.1 using contact less powered startup, an anticollision request can be answered at an earlier stage.

#### 1.2 TOE Overview

#### 1.2.1 TOE Definition and Usage

The TOE consists of smart card ICs (Security Controllers), firmware and user guidance meeting high requirements in terms of performance and security designed by Infineon Technologies AG. This TOE is intended to be used in smart cards for security-relevant applications and as developing platform for smart card operating systems according to the lifecycle model from [1]

The term Smartcard Embedded Software is used in the following for all operating systems and applications stored and executed on the TOE. The TOE is the platform for the Smartcard Embedded Software. The Smartcard Embedded Software itself is not part of the TOE. The TOE does not require any non-TOE hardware/software/firmware.

Security Target Introduction (ASE\_INT)

### 1.2.2 TOE major security features

- Cryptographic support: RNG (PTG.2 according to [6])

- Memory management unit supporting different memory access levels

- Memory encryption

- Robust set of sensors and detectors for the purpose of monitoring proper chip operating conditions

- Security life control

- Bus encryption for security peripherals

- Tearing safe NVM programming

- Security optimized wiring

- Device phase management supporting isolation of test features

- Detection of NVM single and multi bit errors

TOE Description

## 2 TOE Description

The TOE description helps the reader to understand the specific security environment and the security policy. In this context the assets, threats, security objectives and security functional requirements can be employed.

#### 2.1 TOE Components

### 2.1.1 Hardware Components

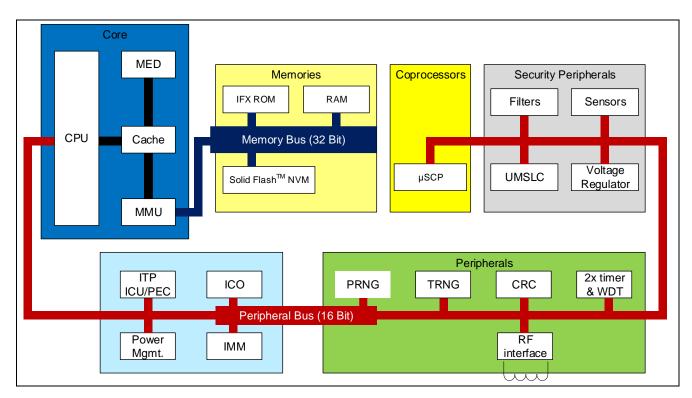

Figure 1 shows a HW block diagram of the M7791 B12:

Figure 1 HW Block diagram of the TOE

The TOE consists of a core system, memories, coprocessor, peripherals, security modules and control peripherals.

The major components of the core system are the non-standard CPU, the MMU (Memory Management Unit) and MED (Memory Encryption/Decryption Unit).

The CPU accesses memory via the integrated Memory Encryption and Decryption unit (MED). All data of the memory block is encrypted. The access rights of the application to the memories can be controlled with the memory management unit (MMU). Errors in RAM and ROM are automatically detected (EDC, Error Detection Code) in terms of the SOLID FLASH™ memory 1-Bit-errors are also corrected (ECC, Error Correction Code). The user software has to be implemented in SOLID FLASH™ memory. The user can choose, whether the software is loaded into the SOLID FLASH™ memory by Infineon Technologies AG or by the user

**TOE Description**

The controller of this TOE stores both code and data in a linear 16-Mbyte memory space, allowing direct access without the need to swap memory segments in and out of memory using a memory management unit.

The cache is a high-speed memory buffer located between the CPU and (external) main memories holding a copy of some of the memory contents to enable access, which is considerably faster than retrieving the information from the main memory. In addition to its fast access speed, the cache also consumes less power than the main memories.

The power management module supports different halt and sleep modes (low activity modes consuming little power) as well as data transmissions using peripheral event channels. Moreover, the current limitation function can be used for power balancing.

The low-power HALT mode is used to reduce the overall power consumption during data transfer between peripherals and volatile memories. The timer can be used to implement timing critical communication protocols. The RF interface is a contactless interface compliant to ISO14443.

The Clock Unit (ICO) supplies the clocks for all components of the TOE. The Clock Unit can work in an internal and external clock mode. When operating in the internal clock mode the system frequency is derived from an internal oscillator, whereas in external clock mode, the system clock is derived from an externally supplied interface clock according to a defined dependency.

The Interrupt and Peripheral Event Channel Controller (ITP) can process interrupt requests from different sources, each with its own subnodes, to determine whether a corresponding interrupt service routine (ISR) is to run or whether data is to be transferred in up to four peripheral event channels.

The Interface Management Module (IMM) monitors the status of all connected interfaces, detects changes in the status of an interface, receives reset requests from an interface, and provides a clock selection and automatic clock switching mechanism for the external clock of the clock unit. Reset, clock and power supply behaviour is managed here.

The controller provides a pseudo RNG (PRNG) for fast random number generation times.

The TRNG (True Random Number Generator) is specially designed for smartcard applications. The TRNG fulfils the requirements of the functionality class PTG.2 of [6] and produces genuine random numbers which then can be used directly or as seed for the PRNG (Pseudo Random Number generator). The PRNG is not in the scope of the evaluation.

The Cyclic Redundancy Check logic (CRC) allows easy generation of checksums according to ISO/IEC 3309 (16-bit CRC).

The timer/counter unit has 2 timers. The unit is used for timer operation when clocked by the oscillator/system clock or counter operation depending on the clock source configured.

The watchdog timer is a circuit that monitors controller operation by automatically initiating a reset if a specified period without an adequate response elapses after occurrence of a hardware or software irregularity.

The security peripherals consist of sophisticated modules, including a UMSLC (user mode security life control), a set of sensors, regulators and filters along with security-optimized wiring to detect faults as well as electrical and physical conditions, and initiate alarms to indicate security breaches. The UMSLC enables the user software to check the activity and proper function of the system's security features.

The micro Symmetric Cryptographic Processor ( $\mu$ SCP) supports calculation of dual-key or triple-key triple-DES and AES. The  $\mu$ SCP provides measures against probing and forcing attacks. However it does not directly contribute to any SFR.

ic TOE Description

The STS (self-test software), RMS (Resource Management System), Service Algorithm Minimal (SAM) and Flash Loader together compose the TOE firmware stored in the ROM. All mandatory functions for internal testing, production usage and start-up behavior (STS), and also the RMS and SAM functions are grouped together in a common privilege level. These privilege levels are protected by a hardwired Memory Management Unit (MMU) setting.

The TOE uses Special Function Registers (SFRs). These SFRs are used for general purposes and chip configuration; they are located in SOLID FLASH™ memory in a configuration area page.

The bus system comprises two separate bus entities: a memory bus and a peripheral bus for high-speed communication with the peripherals.

Security optimized wiring protect certain critical signals.

The following is a list of features provided by the TOE:

- 24-bit linear addressing

- Up to 16 Mbytes of addressable memory

- Register-based architecture (registers can be accessed as bytes, words (2 bytes), and doublewords (4 bytes))

- 2-stage instruction pipeline

- Extensive set of powerful instructions, including 16- and 32-bit arithmetic and logic instructions

- Cache with single-cycle access searching

- 16-bit ALU

### 2.1.2 Firmware and Software components

The entire firmware of the TOE consists of different parts, as described below:

One part comprises the RMS and SAM routines for NVM programming, security functional test, and random number online testing (Resource Management System, IC Dedicated Support Software in PP [1]). The RMS and SAM routines are stored by Infineon Technologies AG in ROM.

The second part is the STS, consisting of test and initialization routines (Self Test Software, IC Dedicated Test Software in PP [1]). The STS routines are stored in a specially protected test ROM and are not accessible by user software with the exception of firmware V77.014.12.1. For this firmware version, the user software is allowed to jump to a dedicated STS area to continue startup after anticollission has been performed.

The third part is the Flash Loader, a piece of software located in ROM and NVM. It supports download of user software or parts of it to NVM. After completion of the download the Flash Loader can be deactivated permanently by the user.

The fourth part is the NRG<sup>TM</sup> software interface, accessible via RMS routines, if the NRG<sup>TM</sup> interface option is active. Note that the NRG<sup>TM</sup> Interface portion is always present but deactivated in case of non- NRG<sup>TM</sup> Interface derivatives. The NRG<sup>TM</sup> software is not part of the TSF and thus not within the scope of the evaluation.

For this TOE, the user can choose between two different firmware packages as shown in Table 1.

### 2.1.3 User Guidance Components

The guidance documentation consists of:

Public TOE Description

- M7791 SOLID FLASH™ Controller for Contactless Transport, Payment and Basic ID Applications Hardware Reference Manual

- AMM Addendum to M7791 Hardware Reference Manual (optional). This addendum document describes the AMM and is only provided in case the configuration option AMM is chosen.

- SLx 70 Family Production and Personalization User's Manual

- SLE 70 Family Programmer's Reference User's Manual

- SLE77 Controller Family Solid Flash™ Controller for Security Applications Errata Sheet

- These documents contain the description of all interfaces of the software to the hardware relevant for programming the TOE.

- M7791 Security Guidelines User's manual: This document provides secure coding guidance to the application writer.

- Option 2 for Fast Startup: this document describes the fast startup option. This document is only delivered to the user in case the firmware version V77.014.12.1 is chosen.

The "SLE77 Controller Family Solid Flash™ Controller for Security Applications - Errata Sheet" may be changed during the life cycle of the TOE. Changes are reported in a monthly updated list [5] provided by Infineon Technologies AG to the user.

Finally the certification report may contain an overview of recommendations to a software developer regarding the secure use of the TOE.

### 2.2 Physical Scope of the TOE

The physical scope of the TOE is defined by the TOE components described in chapter 2.1.

## 2.3 Logical Scope of the TOE

The logical scope of the TOE consists of the logical security features provided by the TOE. These features are listed in chapter 1.2.2. More details are provided in this chapter:

- Cryptographic support: RNG (PTG.2 according to [6])

- Memory management unit supporting six different privilege levels

- Memory encryption: all data of memories ROM, RAM and NVM are encrypted.

- Robust set of sensors and detectors for the purpose of monitoring proper chip operating conditions consisting of a temperature sensor, backside light detector, glitch sensor and low frequency sensor.

- Security life control: a life test on specific security features can be used by the IC embedded software to detect manipulation of these security features

- Bus encryption for security peripherals: All data transfers to and from dedicated peripherals are encrypted dynamically.

- Tearing safe NVM programming: the RMS provides specific routines provided for tearing safe programming. These routines prevent an unspecified interim state by either propagating the pre- or post-programming condition.

- Security optimized wiring: shield lines in combination with layout measures reduce the risk of successful manipulative attacks.

- Device phase management supporting isolation of test features and flash loader accessibility: dedicated test features employed during production are switched off before customer delivery.

- Detection of NVM single and multi bit errors: Single bit errors are detected and corrected and multi bit errors detected.

Public TOE Description

#### 2.4 Interfaces of the TOE

- The physical interface of the TOE to the external environment is the entire surface of the IC.

- The RF interface (radio frequency power and signal interface) enables contactless communication between a PICC (proximity integration chip card, PICC) and a PCD reader/writer (proximity coupling device, PCD). Power supply is received and data are received or transmitted by an antenna which consists of a coil with a few turns directly connected to the IC.

- The interface to the firmware consists of special registers used for hardware configuration and control (Special Function Registers, SFR).

- The interface of the TOE to the operating system is covered by the RMS routines and by the instruction set of the TOE.

- The interface of the TOE to the test routines is formed by the STS test routine call, i.e. entry to test mode (STS-TM entry).

## 2.5 Forms of Delivery

The TOE can be delivered in the form of complete modules, as plain wafers in an IC case (e.g. DS020) or in bare dies. The delivery can therefore be at the end of phase 3 or at the end of phase 4 which may also include pre-personalization steps according to [1]. In any case the testing of the TOE is finished and the extended test features are removed. From a security policy point of view the different forms of delivery do not have any impact.

The delivery to the software developer (phase  $2 \rightarrow$  phase 1) contains the development package, which is delivered in electronic form. It contains the documents as described above, the development and debugging tools.

Part of the software delivery is the Flash Loader program, provided by Infineon Technologies AG, running on the TOE and controlling the download of user software onto the TOE via the UART interface. The download is only possible after successful authentication. The user software can also be downloaded in an encrypted way. In addition, the user can permanently block further use of the Flash Loader.

The table as follows provides an overview about form and method of TOE deliveries:

Table 2 TOE deliveries: forms and methods

| TOE Component                                             | Delivered<br>Format         | Delivery Method                  | Comment                                                               |

|-----------------------------------------------------------|-----------------------------|----------------------------------|-----------------------------------------------------------------------|

| Hardware                                                  |                             |                                  |                                                                       |

| M7791 B12                                                 | Wafer, IC case,<br>packages | Postal transfer in cages         | All materials are delivered to distribution centers in cages, locked. |

| Firmware                                                  |                             |                                  |                                                                       |

| All (see Table 1 "firmware")                              | -                           | -                                | stored on the delivered hardware.                                     |

| Guidance Documentation                                    |                             |                                  |                                                                       |

| All User Guidance documents (see Table 1 "User Guidance") | Paperless<br>document       | Secured<br>download <sup>1</sup> | _                                                                     |

Public Security Target Lite 11 1.3

<sup>&</sup>lt;sup>1</sup> Secured download is a way of delivery of documentation and TOE related software using a secure ishare connected to Infineon customer portal. The TOE user needs a DMZ Account to login (authenticate) via the Internet.

Public TOE Description

#### 2.6 Production sites

The TOE may be handled at different production sites but the silicon is produced in Dresden or Globalfoundries only. To distinguish the different production sites of various products in the field, the site is coded in the Generic Chip Ident Mode data. The exact coding of the relevant Generic chip identification data is described in M7791 Hardware Reference Manual. The TOE is produced in Dresden.

The delivery measures are described in the ALC\_DVS aspect.

### 2.7 TOE Configuration

This TOE is represented by various configurations called products.

The module design, layout and footprint, of all products are identical. However, minor differences between one metal mask allows the TOE to connect to different types of antennas (not part of the TOE). The metal masks differ in their input capacities of the RFI peripheral.

The degree of freedom for configuring the TOE is predefined by Infineon Technologies AG.

The table as follows shows the TOE hardware configurations such as the maximum configurable memory sizes and availability of cryptographic coprocessors.

**TOE Description**

**Table 3** TOE hardware configuration options

| up to 100 kBytes up to 4 kBytes  Available/unavailable  Available/unavailable  27pF, 56pF, 78pF                          |  |

|--------------------------------------------------------------------------------------------------------------------------|--|

| up to 4 kBytes  Available/unavailable  Available/unavailable                                                             |  |

| up to 4 kBytes  Available/unavailable  Available/unavailable                                                             |  |

| Available/unavailable                                                                                                    |  |

| Available/unavailable                                                                                                    |  |

| -                                                                                                                        |  |

| -                                                                                                                        |  |

| 27pF, 56pF, 78pF                                                                                                         |  |

|                                                                                                                          |  |

|                                                                                                                          |  |

| Available/unavailable                                                                                                    |  |

| Available/unavailable                                                                                                    |  |

|                                                                                                                          |  |

| Available/unavailable                                                                                                    |  |

| Available/unavailable                                                                                                    |  |

|                                                                                                                          |  |

|                                                                                                                          |  |

| 33MHz to HIGH                                                                                                            |  |

|                                                                                                                          |  |

| V77.014.11.2 or                                                                                                          |  |

| V77.014.12.1                                                                                                             |  |

| i) the values for FLASH_MAXSIZE, RAM_MAXSIZE and CAPA_VALUES are defined in [8] ii) the value for HIGH is defined in [7] |  |

|                                                                                                                          |  |

Two methods are available to customers to configure the TOE:

- 1. To order a configuration, which is defined and offered by Infineon Technologies.

- 2. To apply the Bill-Per-Use (BPU) method for the TOE. This method enables a customer to use tailored products of the TOE within the TOE's configuration options

BPU allows a customer to block chips on demand at the customer's premises. Customers, who intend to use this feature receive the TOEs in a predefined configuration, e.g. no blocking applied. The blocking information is part of a chip configuration area. The blocking information can be modified by customers using specific APDUs. Once final blocking is done, further modifications are disabled.

The BPU software part is only present on predefined products, which have been ordered with the BPU option. In all other cases this software is not present on the product.

TOE Description

### 2.7.1 TOE initialization with Customer Software

This TOE is equipped with Flash Loader software (FL) to download user software, i.e. an operating system and applications. Various options can be chosen by the user to store software onto the SOLID FLASH™:

Table 4 Options to initialize the TOE with customer software

| Case | Option                                                                                                                                                                       | Flash Loader Status                                                                                                                                                                                                                                                       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | The user provides software to download into the SOLID FLASH™ memory to Infineon Technologies AG. The software is loaded into the SOLID FLASH™ memory during chip production. | There is no Flash Loader present.                                                                                                                                                                                                                                         |

| 2    | The user provides software to download into the SOLID FLASH™ memory to Infineon Technologies AG. The software is loaded into the NVM memory during chip production.          | The Flash Loader is blocked by Infineon but can be activated or reactivated by the user or subcontractor to download software into the SOLID FLASH™ memory. The user is required to provide a reactivation procedure as part of the software to Infineon Technologies AG. |

2021-10-27

Conformance Claims (ASE\_CCL)

#### 3 Conformance Claims (ASE\_CCL)

#### 3.1 **CC Conformance Claim**

This Security Target Lite (ST) and the TOE claim conformance to Common Criteria version v3.1 part 1 [2], part 2 [3] and part 3 [4].

Conformance of this ST is claimed for:

Common Criteria part 2 extended and Common Criteria part 3 conformant.

#### 3.2 PP Claim

This Security Target Lite claims strict conformance to [1].

The Security IC Platform Protection Profile with Augmentation Packages is registered and certified by the Bundesamt für Sicherheit in der Informationstechnik<sup>1</sup> (BSI) under the reference:

BSI-CC-PP-0084-2014, Version 1.0, dated 2014-01-13.

The security assurance requirements of the TOE are according to the Security IC Platform Protection Profile [1]. They are all drawn from Part 3 of the Common Criteria version v3.1.

The augmentations of the PP [1] are listed below.

Augmentations of the assurance level of the TOE Table 5

| Assurance Class          | Assurance components | Description                                |

|--------------------------|----------------------|--------------------------------------------|

| Life-cycle<br>support    | ALC_DVS.2            | Sufficiency of security measures           |

| Vulnerability assessment | AVA_VAN.5            | Advanced methodical vulnerability analysis |

#### 3.3 **Package Claim**

This Security Target Lite claims conformance to following functional packages from [1]:

• Package Loader dedicated for usage in secured environment only; section 7.3.1: package conformant

The assurance level for the TOE is EAL5 augmented with the components ALC\_DVS.2 and AVA\_VAN.5.

<sup>1</sup> Bundesamt für Sicherheit in der Informationstechnik (BSI) is the German Federal Office for Information Security **Public Security Target Lite** 15

Conformance Claims (ASE\_CCL)

#### 3.4 Conformance Rationale

This Security Target Lite claims strict conformance to [1].

The Target of Evaluation (TOE) is a typical security IC as defined in [1] chapter 1.2.2 comprising:

- the circuitry of the IC (hardware including the physical memories),

- configuration data, initialisation data related to the IC Dedicated Software and the behaviour of the security functionality

- the IC Dedicated Software with the parts

- the IC Dedicated Test Software,

- the IC Dedicated Support Software.

The TOE is designed, produced and/or generated by the TOE Manufacturer.

### 3.4.1 Security Problem Definition:

The security problem definition of [1] is enhanced by adding a threat. Including this add-on, the security problem definition of this Security Target Lite is consistent with the statement of the security problem definition in [1], as the Security Target Lite claims strict conformance to [1].

#### 3.4.2 Conformance Rationale:

The threat memory access violation T.Mem-Access, due to specific TOE memory access control functionality, has been added. This add-on has no impact on the conformance statements regarding CC [2] and PP [1], with following rational:

The Security Target Lite remains conformant to CC [2], claim 482 as the possibility to introduce additional restrictions is given.

## 3.4.3 Adding Objective

Due to an additional security functionality regarding memory access control - O.Mem-Access, an additional security objective has been introduced. This add-on has no impact on the conformance statements regarding CC [2] and PP [1], with following rational:

The Security Target Lite remains conformant to CC [2], claim 576 as the possibility to introduce additional restrictions is given.

#### 3.4.4 Loader

The PP [1] implements the optional policy for applying a Loader. The Loader is used to load data into the SOLID FLASH™ NVM. The Loader policy defines the Package 1 P.LIM\_Block\_Loader where the Loader is dedicated for usage in secure environment only. This TOE provides a Loader complying with this optional package 1 as outlined in chapter 7.2. Due to these optional additional security functionalities the security objectives O.Cap\_Avail\_Loader, Capability and availability of the Loader, and for the environment OE.Lim\_Block\_Loader, Limitation of capability and blocking the Loader, have been introduced. These addons have no impact on the conformance statements regarding CC [2] and PP [1], with following rational:

The Security Target Lite fulfills the strict conformance claim of the PP [1] due to the application notes 5 applying here. By this note the addition of further security functions and security services are covered, even without deriving particular security functionality from a threat or a policy

Conformance Claims (ASE\_CCL)

### 3.4.5 Summary

Due to the above rational, the security objectives of this Security Target Lite are consistent with the statement of the security objectives in [1], as the Security Target Lite claims package-augmentation to [1].

All security functional requirements defined in [1] are included and completely defined in this ST.

The following security functional requirements are taken from [3] in addition to the SFRs defined in [1]:

FMT\_MSA.1 "Management of security attributes"

FMT\_MSA.3 "Static attribute initialization"

FMT\_SMF.1 "Specification of Management functions"

The security functional requirements as follows are included and completely defined in this ST, section 6:

• FPT\_TST.2 "Subset TOE security testing" (Requirement from [1])

The security functional requirements as follows are added:

• FDP\_ACC.1 "Subset access control"

• FDP\_ACF.1 "Security attribute based access control"

All assignments and selections of the security functional requirements are either done in [1] or in this Security Target Lite.

## 3.5 Application Notes

The functional requirement FCS\_RNG.1 is a refinement of the FCS\_RNG.1 defined in the Protection Profile [1] according to "Anwendungshinweise und Interpretationen zum Schema (AIS)" [6].

Security **Problem Definition (ASE\_SPD)**

## 4 Security Problem Definition (ASE\_SPD)

The content of [1] applies to this chapter completely.

#### 4.1 Threats

The threats are directed against the assets and/or the security functions of the TOE. For example, certain attacks are only one step towards a disclosure of assets while others may directly lead to a compromise of the application security. The more detailed description of specific attacks is given later on in the process of evaluation and certification. An overview on attacks is given in PP [1] section 3.2.

The threats to security are defined and described in PP [1] sections 3.2.

Table 6 Threats according to [1]

| T.Phys-Manipulation | Physical Manipulation                   |

|---------------------|-----------------------------------------|

| T.Phys-Probing      | Physical Probing                        |

| T.Malfunction       | Malfunction due to Environmental Stress |

| T.Leak-Inherent     | Inherent Information Leakage            |

| T.Leak-Forced       | Forced Information Leakage              |

| T.Abuse-Func        | Abuse of Functionality                  |

| T.RND               | Deficiency of Random Numbers            |

### 4.1.1 Additional Threat due to TOE specific Functionality

The additional functionality of introducing sophisticated privilege levels and access control allows the secure separation between the operation system(s) and applications, the secure downloading of applications after personalization and enables multitasking by separating memory areas and performing access controls between different applications. Due to this additional functionality "area based memory access control" a new threat is introduced.

The Smartcard Embedded Software is responsible for its User Data according to the assumption "Treatment of User Data (A.Resp-Appl)". However, the Smartcard Embedded Software may comprise different parts, for instance an operating system and one or more applications. In this case, such parts may accidentally or deliberately access data (including code) of other parts, which may result in a security violation.

The TOE shall avert the threat "Memory Access Violation (T.Mem-Access)" as specified below.

T.Mem-Access Memory Access Violation

Parts of the Smartcard Embedded Software may cause security violations by accidentally or deliberately accessing restricted data (which may include code) or privilege levels. Any restrictions are defined by the security policy of the specific application context and must be implemented by the Smartcard Embedded Software.

Table 7 Additional threats due to TOE specific functions and augmentations

| -            |                         |

|--------------|-------------------------|

| T.Mem-Access | Memory Access Violation |

Security Problem Definition (ASE\_SPD)

## 4.1.2 Assets regarding the Threats

The asset description from PP [1] section 3.1 applies.

## 4.2 Organizational Security Policies

The organizational policy from [1] section 3.3 and section 7.3.1 is applicable.

#### Table 8 Organizational Security Policies according PP [1]

| P.Process-TOE      | Protection during TOE Development and Production |

|--------------------|--------------------------------------------------|

| P.Lim_Block_Loader | Limiting and Blocking the Loader Functionality   |

## 4.3 Assumptions

The TOE assumptions about the operational environment are defined and described in PP [1] section 3.4.

#### Table 9 Table 1: Assumption according PP [1]

| A.Process-Sec-IC | Protection during Packaging, Finishing and Personalization |

|------------------|------------------------------------------------------------|

| A.Resp-Appl      | Treatment of User Data                                     |

Security objectives (ASE\_OBJ)

## 5 Security objectives (ASE\_OBJ)

This section shows the security objectives, which are relevant to the TOE.

### 5.1 Security objectives of the TOE

The security objectives of the TOE are defined and described in PP [1] sections 4.1 and 7.3.1.

Table 10 Objectives for the TOE according to PP [1]

| O.Phys-Manipulation | Protection against Physical Manipulation        |

|---------------------|-------------------------------------------------|

| O.Phys-Probing      | Protection against Physical Probing             |

| O.Malfunction       | Protection against Malfunction                  |

| O.Leak-Inherent     | Protection against Inherent Information Leakage |

| O.Leak-Forced       | Protection against Forced Information Leakage   |

| O.Abuse-Func        | Protection against Abuse of Functionality       |

| O.Identification    | TOE Identification                              |

| O.RND               | Random Numbers                                  |

| O.Cap_Avail_Loader  | Capability and availability of the Loader       |

The TOE shall provide "Area based Memory Access Control (O.Mem-Access)" as specified below.

O.Mem-Access Area based Memory Access Control

The TOE must provide the Smartcard Embedded Software with the capability to define restricted access memory areas. The TOE must then enforce the partitioning of such memory areas so that access of software to memory areas and privilege levels is controlled as required, for example, in a multi-application environment.

Table 11 Additional objectives due to TOE specific functions and augmentations

| O.Mem-Access | Area based Memory Access Control |

|--------------|----------------------------------|

|              |                                  |

### 5.2 Security Objectives for the development and operational Environment

The security objectives from [1] section 4.2, 4.3 and 7.3.1 are applicable for this TOE.

The table below lists the environmental security objectives.

Table 12 Security objectives for the environment according to [1]

| OE.Resp-Appl        | Treatment of User Data                            |

|---------------------|---------------------------------------------------|

| OE.Process-Sec-IC   | Protection during composite product manufacturing |

| OE.Lim_Block_Loader | Limitation of capability and blocking the Loader  |

Security objectives (ASE\_OBJ)

#### 5.3 Security Objectives Rationale

The security objectives rationale of the TOE is defined and described in PP [1] section 4.4 and 7.3.1.

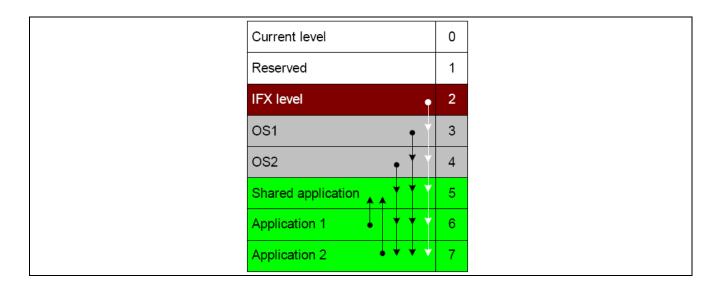

Compared to the [1] an enhancement regarding memory area protection has been established. The clear definition of privilege levels for operated software establishes the clear separation of different restricted memory areas for running the firmware, downloading and/or running the operating system and to establish a clear separation between different applications. Nevertheless, it is also possible to define a shared memory section where separated applications may exchange defined data. The privilege levels clearly define by using a hierarchical model the access right from one level to the other. These measures ensure that the threat T.Mem-Access is clearly covered by the security objective O.Mem-Access.

The objective O.Cap\_Avail\_Loader and the organizational policy P.Lim\_Block\_Loader as described in [1] chapter 7.3.1 apply only to TOE products with Flash Loader enabled for software or data download by the user. In other cases the Flash Loader is not available anymore and the user software or data download is completed.

Extended Component Definition (ASE\_ECD)

## 6 Extended Component Definition (ASE\_ECD)

There are several extended components defined and described for the TOE:

- the family FCS\_RNG at the class FCS Cryptographic Support

- the family FMT\_LIM at the class FMT Security Management

- the family FAU\_SAS at the class FAU Security Audit

- the family FDP\_SDC at the class FDP User Data Protection

- the family FPT\_TST.2 at the class FPT Protection of the TSF

The extended families FCS\_RNG, FMT\_LIM, FAU\_SAS and FDP\_SDC are defined and described in PP [1] section 5. The component FPT\_TST.2 is defined in the following sections.

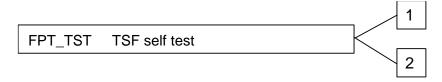

## 6.1 Component "Subset TOE security testing (FPT\_TST)"

The security is strongly dependent on the correct operation of the security functions. Therefore, the TOE shall support that particular security functions or mechanisms are tested in the operational phase (Phase 7). The tests can be initiated by the Smartcard Embedded Software and/or by the TOE or is done automatically and continuously.

Part 2 of the Common Criteria provides the security functional component "TSF testing (FPT\_TST.1)". The component FPT\_TST.1 provides the ability to test the TSF's correct operation.

For the user it is important to know which security functions or mechanisms can be tested. The functional component FPT\_TST.1 does not mandate to explicitly specify the security functions being tested. In addition, FPT\_TST.1 requires verification of the integrity of TSF data and of the stored TSF executable code which might violate the security policy. Therefore, the functional component "Subset TOE security testing (FPT\_TST.2)" of the family TSF self test has been newly created. This component allows that particular parts of the security mechanisms and functions provided by the TOE are tested.

### 6.2 Definition of FPT\_TST.2

The functional component "Subset TOE security testing (FPT\_TST.2)" has been newly created (Common Criteria Part 2 extended). This component allows that particular parts of the security mechanisms and functions provided by the TOE can be tested after TOE Delivery or are tested automatically and continuously during normal operation transparent for the user.

This security functional component is used instead of the functional component FPT\_TST.1 from Common Criteria Part 2. For the user it is important to know which security functions or mechanisms can be tested. The functional component FPT\_TST.1 does not mandate to explicitly specify the security functions being tested. In addition, FPT\_TST.1 requires verifying the integrity of TSF data and stored TSF executable code which might violate the security policy.

The functional component "Subset TOE testing (FPT\_TST.2)" is specified as follows (Common Criteria Part 2 extended).

Extended Component Definition (ASE\_ECD)

## 6.3 TSF self test (FPT\_TST)

Family Behavior The Family Behavior is defined in [3] section 15.14 (442,443).

Component levelling

FPT\_TST.1: The component FPT\_TST.1 is defined in [3] section 15.14 (444, 445,446).

FPT\_TST.2: Subset TOE security testing, provides the ability to test the correct operation of particular

security functions or mechanisms. These tests may be performed at start-up, periodically, at the request of the authorized user, or when other conditions are met. It also provides the

ability to verify the integrity of TSF data and executable code.

Management: FPT\_TST.2

The following actions could be considered for the management functions in FMT:

management of the conditions under which subset TSF self testing occurs, such as during initial startup, regular interval or under specified conditions

• management of the time of the interval appropriate.

Audit: FPT\_TST.2

There are no auditable events foreseen.

FPT\_TST.2 Subset TOE testing

Hierarchical to: No other components.

Dependencies: No dependencies

FPT\_TST.2.1: The TSF shall run a suite of self tests [selection: during initial start-up, periodically during normal operation, at the request of the authorized user, and/or at the conditions

[assignment: conditions under which self test should occur]] to demonstrate the correct

operation of [assignment: functions and/or mechanisms].

## 7 Security Requirements (ASE\_REQ)

For this section [1] section 6 can be applied completely.

## 7.1 TOE Security Functional Requirements

The security functional requirements (SFR) for the TOE are defined and described in [1] section 6.1 and section 7.3.1 and in the following description.

Table 13 provides an overview of the functional security requirements of the TOE, defined in [1] section 6.1 and section 7.3.1. Any refinements are also valid for this ST.

FCS\_RNG.1 "Random number generation"

Table 13 Security functional requirements of the TOE defined in PP [1]

| Security Fund | Security Functional Requirement               |  |  |

|---------------|-----------------------------------------------|--|--|

| FRU_FLT.2     | "Limited fault tolerance"                     |  |  |

| FPT_FLS.1     | "Failure with preservation of secure state"   |  |  |

| FMT_LIM.1     | "Limited capabilities"                        |  |  |

| FMT_LIM.2     | "Limited availability"                        |  |  |

| FAU_SAS.1     | "Audit storage"                               |  |  |

| FDP_SDC.1     | "Stored data confidentiality                  |  |  |

| FDP_SDI.2     | "Stored data integrity monitoring and action" |  |  |

| FPT_PHP.3     | "Resistance to physical attack"               |  |  |

| FDP_ITT.1     | "Basic internal transfer protection"          |  |  |

| FPT_ITT.1     | "Basic internal TSF data transfer protection  |  |  |

| FDP_IFC.1     | "Subset information flow control"             |  |  |

| FCS_RNG.1     | "Random number generation"                    |  |  |

| FMT_LIM.1/L   | Loader "Limited capabilities"                 |  |  |

| FMT_LIM.2/L   | Loader "Limited availability"                 |  |  |

Table 14 provides an overview about security functional requirements, which are added to the TOE. All requirements are taken from [3] Part 2, with the exception of requirement FPT\_TST.2, which is defined in this ST completely.

Table 14

Additional security functional requirements of the TOE

| Security Functional Requirement |                                           |  |

|---------------------------------|-------------------------------------------|--|

| FPT_TST.2                       | "Subset TOE security testing"             |  |

| FDP_ACC.1                       | "Subset access control"                   |  |

| FDP_ACF.1                       | "Security attribute based access control" |  |

| FMT_MSA.1                       | "Management of security attributes"       |  |

| FMT_MSA.3                       | "Static attribute initialisation"         |  |

| FMT_SMF.1                       | "Specification of Management functions"   |  |

All assignments and selections of the security functional requirements of the TOE are done in [1] and in the following description.

The above marked extended components FMT\_LIM.1 and FMT\_LIM.2 are introduced in [1] to define the IT security functional requirements of the TOE as an additional family (FMT\_LIM) of the Class FMT (Security Management). This family describes the functional requirements for the Test Features of the TOE. The new functional requirements were defined in the class FMT because this class addresses the management of functions of the TSF.

The additional component FAU\_SAS is introduced to define the security functional requirements of the TOE of the Class FAU (Security Audit). This family describes the functional requirements for the storage of audit data and is described in the next chapter.

The requirement FPT\_TST.2 is the subset of TOE testing and originated in [3]. This requirement is given as the correct operation of the security functions is essential. The TOE provides mechanisms to cover this requirement by the smartcard embedded software and/or by the TOE itself.

### 7.1.1 Definition required by [1]

According to [1] Application Note 14 the term "secure state" used by FPT\_FLS.1 shall be described and a definition should be provided.

#### Definition of secure state:

Secure state describes three different conditions of the TOE:

- 1. the controller ceases operation. This condition can only be resolved by a cold or warm start of the controller. It is triggered by a security reset.

- 2. the controller enters a security trap. The trap handler can be defined by the user. In case no trap handler is provided the first condition is entered.

- 3. in case of a sudden power loss of the TOE during NVM programming (tearing): the TOE is in a condition to either restore the old NVM content or to start with the new programmed value.

Note: a security reset invalidates the RAM content.

According to [1] Application Note 15, "The Common Criteria suggest that the TOE generates audit data for the security functional requirements Limited fault tolerance (FRU\_FLT.2) and Failure with preservation of secure state (FPT\_FLS.1)." In case of the first two conditions no Audit data are collected, because the effect entering the secure state is immediately visible. For the third condition indirect audit data is available, i.e. the user can check, whether new or old NVM data is available.

### 7.1.2 Extended Components FCS\_RNG.1 and FAU\_SAS.1

#### 7.1.2.1 FCS\_RNG

To define the IT security functional requirements of the TOE an additional family (FCS\_RNG) of the Class FCS (cryptographic support) is defined in [1]. This family describes the functional requirements for random number generation used for cryptographic purposes.

#### FCS\_RNG.1 Random Number Generation

Hierarchical to: No other components

Dependencies: No dependencies

FCS\_RNG.1 Random numbers generation Class PTG.2 according to [6]

| FCS_RNG.1.1 The TSF shall provide a physical random number generator that implements | FCS RNG.1.1 | The TSF shall r | provide a physica | l random number | generator that implements |

|--------------------------------------------------------------------------------------|-------------|-----------------|-------------------|-----------------|---------------------------|

|--------------------------------------------------------------------------------------|-------------|-----------------|-------------------|-----------------|---------------------------|

| PTG.2.1 | A total failure test detects a total failure of entropy source immediately |

|---------|----------------------------------------------------------------------------|

|         | when the RNG has started. When a total failure is detected, no random      |

|         | numbers will be output.                                                    |

PTG.2.2 If a total failure of the entropy source occurs while the RNG is being operated, the RNG prevents the output of any internal random number that depends on some raw random numbers that have been generated after the total failure of the entropy source.

PTG.2.3 The online test shall detect non-tolerable statistical defects of the raw random number sequence (i) immediately when the RNG has started, and (ii) while the RNG is being operated. The TSF must not output any random numbers before the power-up online test has finished successfully or when a defect has been detected.

PTG.2.4 The online test procedure shall be effective to detect non-tolerable weaknesses of the random numbers soon.

PTG.2.5 The online test procedure checks the quality of the raw random number sequence. It is triggered continuously. The online test is suitable for detecting non-tolerable statistical defects of the statistical properties of the raw random numbers within an acceptable period of time.

#### FCS\_RNG.1.2 The TSF shall provide numbers in the format 8- or 16-bit that meet

PTG.2.6 Test procedure A, as defined in [6] does not distinguish the internal random numbers from output sequences of an ideal RNG.

PTG.2.7 The average Shannon entropy per internal random bit exceeds 0.997.

Note: The physical random number generator implements total failure testing of the random source data and a continuous random number generator test according to:

National Institute of Standards and Technology, Security Requirements for Cryptographic Modules, Federal Information Processing Standards Publication (FIPS) 140-2, 2002-03-12, chapter 4.9.2

#### 7.1.2.2 FAU SAS

The PP [1] defines additional security functional requirements with the family FAU\_SAS of the class FAU (Security Audit). This family describes the functional requirements for the storage of audit data. It has a more general approach than FAU\_GEN, because it does not necessarily require the data to be generated by the TOE itself and because it does not give specific details of the content of the audit records.

The TOE shall meet the requirement "Audit storage (FAU\_SAS.1)" as specified below (Common Criteria Part 2 extended).

#### FAU\_SAS.1 Audit Storage

Hierarchical to: No dependencies

Dependencies: No dependencies.

FAU\_SAS.1.1 The TSF shall provide the test process before TOE Delivery with the capability to store the Initialization Data and/or Pre-personalization Data and/or supplements of the Security IC Embedded Software in the not changeable configuration page area and non-volatile memory.

### 7.1.3 Subset of TOE testing

The security is strongly dependent on the correct operation of the security functions. Therefore, the TOE shall support that particular security functions or mechanisms are tested in the operational phase (Phase 7). The tests can be initiated by the Smartcard Embedded Software and/or by the TOE.

The TOE shall meet the requirement "Subset TOE testing (FPT\_TST.2)" as specified below (Common Criteria Part 2 extended).

#### FPT\_TST.2 Subset TOE testing

Hierarchical to: No other components.

Dependencies: No dependencies

FPT\_TST.2.1 The TSF shall run a suite of self tests <u>at the request of the authorised user</u> to demonstrate the correct operation of <u>the alarm lines and/or following environmental sensor</u> mechanisms:

- CORE CPU related alarms

- Temperature alarm

- Memory Bus

- NVM\_MISS SOLID FLASH™ memory illegal addressing alarm

- FSE Internal Frequency Sensor alarm

- Light Light sensitive alarm

- WDT Watch Dog Timer related alarms

- SW Software triggered alarm

- TRNG True Random Number Generator

- Glitch sensor alarm

- Backside light detection (BLD) alarm

- RAM/ROM EDC or SOLID FLASH™ memory ECC

## 7.1.4 Memory access control

Usage of multiple applications in one Smartcard often requires code and data separation in order to prevent one application from accessing code and/or data of another application. For this reason the TOE provides Area based Memory Access Control. The underlying memory management unit (MMU) is documented in the M7791 Hardware Reference Manual.

The security service being provided is described in the Security Function Policy (SFP) Memory Access Control Policy. The security functional requirement "Subset access control (FDP\_ACC.1)" requires that this policy is in place and defines the scope were it applies. The security functional requirement "Security attribute based access control (FDP\_ACF.1)" defines security attribute usage and characteristics of policies. It describes the rules for the function that implements the Security Function Policy (SFP) as identified in FDP\_ACC.1. The decision whether an access is permitted or not is taken based upon attributes allocated to

the software. The Smartcard Embedded Software defines the attributes and memory areas. The corresponding permission control information is evaluated "on-the-fly" by the hardware so that access is granted/effective or denied/inoperable.

The security functional requirement "Static attribute initialisation (FMT\_MSA.3)" ensures that the default values of security attributes are appropriately either permissive or restrictive in nature. Alternative values can be specified by any subject provided that the Memory Access Control Policy allows that. This is described by the security functional requirement "Management of security attributes (FMT\_MSA.1)". The attributes are determined during TOE manufacturing (FMT\_MSA.3) or set at run-time (FMT\_MSA.1).

From TOE's point of view the different roles in the Smartcard Embedded Software can be distinguished according to the memory based access control. However the definition of the roles belongs to the user software.

The following Security Function Policy (SFP) Memory Access Control Policy is defined for the requirement "Security attribute based access control (FDP\_ACF.1)":

#### **Memory Access Control Policy**

The TOE shall control read, write, delete and execute accesses of software running at the privilege levels as defined below. Any access is controlled, regardless whether the access is on code or data or a jump on any other privilege level outside the current one.

The memory model provides distinct, independent privilege levels separated from each other in the virtual address space. These levels are referred to as the Infineon Technologies (IFX) level, operating system 1 and 2 levels (OS1, OS2), shared application level, and application 1 and 2 levels. A pseudo-level is the "current" level, which is simply the level on which code is currently being executed. The access rights are controlled by the MMU and related to the privilege level as depicted in following diagram:

Figure 2 Privilege Levels of the TOE

The TOE shall meet the requirement "Subset access control (FDP\_ACC.1)" as specified below.

#### FDP\_ACC.1 Subset access control

Hierarchical to: No other components.

Dependencies: FDP\_ACF.1 Security attribute based access control

FDP\_ACC.1.1 The TSF shall enforce the Memory Access Control Policy on all subjects (software running at the defined and assigned privilege levels), all objects (data including code stored in memories) and all the operations defined in the Memory Access Control Policy, i.e. privilege levels.

The TOE shall meet the requirement "Security attribute based access control (FDP\_ACF.1)" as specified below.

#### FDP\_ACF.1 Security attribute based access control

Hierarchical to: No other components.

Dependencies: FDP\_ACC.1 Subset access control

FMT\_MSA.3 Static attribute initialisation

FDP ACF.1.1 The TSF shall enforce the Memory Access Control Policy to objects based on the following:

#### Subject:

- software running at the IFX, OS1 and OS2 privilege levels required to securely operate the chip. This includes also privilege levels running interrupt routines.

- software running at the privilege levels containing the application software

#### Object:

data including code stored in memories

#### Attributes:

- the memory area where the access is performed to and/or

- the operation to be performed.

- FDP\_ACF.1.2 The TSF shall enforce the following rules to determine if an operation among controlled subjects and controlled objects is allowed:

evaluate the corresponding permission control information of the relevant memory range before, during or after the access so that accesses to be denied cannot be utilised by the subject attempting to perform the operation.

- FDP\_ACF.1.3 The TSF shall explicitly authorize access of subjects to objects based on the following additional rules: none.

- FDP\_ACF.1.4 The TSF shall explicitly deny access of subjects to objects based on the following additional rules:

none.

The TOE shall meet the requirement "Static attribute initialisation (FMT\_MSA.3)" as specified below.

#### FMT\_MSA.3 Static attribute initialisation

Hierarchical to: No other components.

Dependencies: FMT\_MSA.1 Management of security attributes

FMT\_SMR.1 Security roles

FMT\_MSA.3.1 The TSF shall enforce the <u>Memory Access Control Policy</u> to provide <u>well defined</u> default values for security attributes that are used to enforce the SFP.

FMT\_MSA.3.2 The TSF shall allow <u>any subject, provided that the Memory Access Control Policy is</u>

enforced and the necessary access is therefore allowed<sup>2</sup>, to specify alternative initial values to override the default values when an object or information is created.

The TOE shall meet the requirement "Management of security attributes (FMT\_MSA.1)" as specified below:

#### FMT\_MSA.1 Management of security attributes

Hierarchical to: No other components.

Dependencies: [FDP\_ACC.1 Subset access control or

FDP\_IFC.1 Subset information flow control]

FMT\_SMF.1 Specification of management functions

FMT\_SMR.1 Security roles

FMT\_MSA.1.1 The TSF shall enforce the Memory Access Control Policy to restrict the ability to change

<u>default, modify or delete</u> the security attributes <u>permission control information to the</u>

software running on the privilege levels.

The TOE shall meet the requirement "Specification of management functions (FMT\_SMF.1)" as specified below:

#### FMT\_SMF.1 Specification of management functions

Hierarchical to: No other components

Dependencies: No dependencies

FMT\_SMF.1.1 The TSF shall be capable of performing the following security management functions:

access the configuration registers of the MMU.

<sup>&</sup>lt;sup>1</sup> The static definition of the access rules is documented in the M7791 Hardware Reference Manual

<sup>&</sup>lt;sup>2</sup> The Smartcard Embedded Software is intended to set the memory access control policy

### 7.1.6 Data Integrity

The TOE shall meet the requirement "Stored data integrity monitoring and action (FDP\_SDI.2)" as specified below:

FDP\_SDI.2 Stored data integrity monitoring and action

Hierarchical to: FDP\_SDI.1 stored data integrity monitoring

Dependencies: No dependencies

$FDP\_SDI.2.1 \hspace{0.5cm} The \hspace{0.1cm} TSF \hspace{0.1cm} shall \hspace{0.1cm} monitor \hspace{0.1cm} user \hspace{0.1cm} data \hspace{0.1cm} stored \hspace{0.1cm} in \hspace{0.1cm} containers \hspace{0.1cm} controlled \hspace{0.1cm} by \hspace{0.1cm} the \hspace{0.1cm} TSF \hspace{0.1cm} for \hspace{0.1cm} \underline{data}$

<u>integrity</u> and <u>one- and/or more-bit-errors</u> on all objects, based on the following attributes: <u>corresponding EDC value for ROM and RAM, smart parity for Cache and error correction</u>

ECC for the SOLID FLASH™ NVM.

FDP\_SDI.2.2 Upon detection of a data integrity error, the TSF shall <u>correct 1 bit errors in the SOLID</u>

FLASH™ NVM automatically and inform the user about other bit errors.

The TOE shall meet the requirement "Stored data confidentiality (FDP\_SDC.1)" as specified below:

FDP\_SDC.1 Stored data confidentiality

Hierarchical to: No other components

Dependencies: No dependencies

FDP\_SDC.1.1 The TSF shall ensure the confidentiality of the information of the user data while it is stored

in the RAM and SOLID FLASH™ NVM

### 7.2 Support of the Flash Loader

The usage of the Flash Loader is only allowed in secured environment during the production phase. For this reason the TOE shall meet the requirements "Limited capabilities (FMT\_LIM.1/Loader)" as specified below:

FMT\_LIM.1/Loader Limited Capabilities

Hierarchical to: No other components

Dependencies: No other components.

FMT\_LIM.1.1/Loader The TSF shall be designed and implemented in a manner that limits its capabilities

so that in conjunction with "Limited availability (FMT\_LIM.2)" the following policy is enforced: Deploying Loader functionality after <u>permanent deactivation</u> does not allow stored user data to be disclosed or manipulated by unauthorized user.

The TOE shall meet the requirement "Limited availability – Loader (FMT\_LIM.2/Loader)" as specified below:

FMT\_LIM.2/Loader Limited availability - Loader

Hierarchical to: No other components.

Dependencies: FMT\_LIM.1 Limited capabilities.

FMT\_LIM.2.1/Loader The TSF shall be designed in a manner that limits its availability so that in

conjunction with "Limited capabilities (FMT\_LIM.1)" the following policy is enforced: The TSF prevents deploying the Loader functionality after <u>permanent</u>

deactivation.

The security functional requirements FMT\_LIM.1/Loader and FMT\_LIM.2/Loader apply only to TOE products with Flash Loader enabled for software or data download by the user. In other cases the Flash Loader is not available anymore and the user software or data download is completed.

## 7.3 TOE Security Assurance Requirements

The evaluation assurance level is EAL 5 augmented with ALC\_DVS.2 and AVA\_VAN.5. In the following table, the security assurance requirements are given. The augmentation of the assurance components compared to [1] is expressed with bold letters.

**Table 15** Assurance components

| Aspect      | Acronym   | Description                                                                     | Refinement |

|-------------|-----------|---------------------------------------------------------------------------------|------------|

| Development | ADV_ARC.1 | Security Architecture Description                                               | [1]        |

|             | ADV_FSP.5 | Complete semi-formal functional specification with additional error information | [1]        |

|             | ADV_IMP.1 | Implementation representation of the TSF                                        | [1]        |

|             | ADV_INT.2 | Well-structured internals                                                       |            |

|             | ADV_TDS.4 | Semi-formal modular design                                                      |            |

| Aspect                        | spect Acronym Description |                                                          | Refinement |  |

|-------------------------------|---------------------------|----------------------------------------------------------|------------|--|

| Guidance Documents            | AGD_OPE.1                 | Operational user guidance                                | [1]        |  |

|                               | AGD_PRE.1                 | Preparative procedures                                   | [1]        |  |

| Life-Cycle Support            | ALC_CMC.4                 | Production support, acceptance procedures and automation | [1]        |  |

|                               | ALC_CMS.5                 | Development tools CM coverage                            | [1]        |  |

|                               | ALC_DEL.1                 | Delivery procedures                                      | [1]        |  |

|                               | ALC_DVS.2                 | Sufficiency of security measures                         | [1]        |  |

|                               | ALC_LCD.1                 | Developer defined life-cycle model                       |            |  |

|                               | ALC_TAT.2                 | Compliance with implementation standards                 |            |  |

| Security Target<br>Evaluation | ASE_CCL.1                 | Conformance claims                                       |            |  |

|                               | ASE_ECD.1                 | Extended components definition                           |            |  |

|                               | ASE_INT.1                 | ST introduction                                          |            |  |