# NXP Secure Smart Card Controller N7121 with IC Dedicated Software and Crypto Library (R1/R2)

**Security Target Lite**

Rev. 1.8 — 19 January 2021 BSI-DSZ-CC-1136

Evaluation document PUBLIC

#### **Document information**

| Information | Content                                                                                                                                                                                        |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Keywords    | Common Criteria, Security Target, Security IC, N7121                                                                                                                                           |  |

| Abstract    | This document is the Security Target of the NXP Smart Card Controller N7121 with IC Dedicated Software. The document describes the security Functionality provided by the IC and its software. |  |

# **Revision history**

# Table 1. Revision history

| Version | Release date | Change notice                                      |

|---------|--------------|----------------------------------------------------|

| 1.0     | 2018-11-30   | Initial version based on full Security Target v1.4 |

| 1.1     | 2019-05-31   | Updated version based on full Security Target v1.5 |

| 1.2     | 2019-11-05   | Updated version based on full Security Target v1.6 |

| 1.3     | 2020-01-08   | Updated version based on full Security Target v1.7 |

| 1.4     | 2020-07-15   | Updated version based on full Security Target v1.8 |

| 1.5     | 2020-10-20   | Updated version based on full Security Target v1.9 |

| 1.6     | 2020-12-01   | Updated version based on full Security Target v2.0 |

| 1.7     | 2020-12-11   | Updated version based on full Security Target v2.1 |

| 1.8     | 2021-01-19   | Updated version based on full Security Target v2.2 |

# 1 Introduction

#### 1.1 ST reference

Security Target NXP Secure Smart Card Controller N7121 with IC Dedicated Software and Crypto Library, Version 1.8, NXP Semiconductors Germany GmbH, 19 January 2021.

#### 1.2 TOE reference

The TOE is named NXP Secure Smart Card Controller N7121 with IC Dedicated Software and Crypto Library. In this document, the TOE is abbreviated to N7121. All components of the TOE and their respective version numbers are listed in <u>Section 1.4.1</u>.

#### 1.3 TOE overview

The TOE is the hard macro NXP Secure Smart Card Controller N7121 with IC Dedicated Software and Crypto Library, or in short N7121, which is manafactured in GlobalFoundries 40nm (C40) technology and comprises of hardware, software (security IC Dedicated Software), and documentation. The N7121 is self-sufficient at the boundary of the hard macro and can be instantiated within packaged products. The TOE does not include a customer-specific Security IC Embedded Software, however, it provides secure mechanisms for customers to download and execute their code on the TOE. For the sake of simplicity, in this Security Target, we refer to the IC hardware as the hardware instantiation of the hard macro.

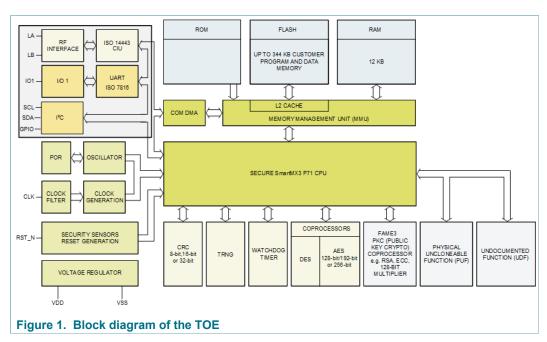

#### 1.3.1 Hardware

The IC hardware is a microcontroller incorporating a central processing unit (CPU), memories accessible via a Memory Management Unit (MMU), cryptographic coprocessors, other security components, contact-based and contactless communication interfaces as well as a general purpose I/O interface which can be used to directly use peripherals of the TOE such as the cryptographic coprocessors. The central processing unit supports a 32-/16-bit instruction set optimized for smart card applications. Onchip memories are ROM, RAM and Flash. The Flash can be used as data or program memory. It consists of highly reliable memory cells, which are designed to provide data integrity. The Flash memory is optimized for applications that require reliable non-volatile data storage for data and program code. Dedicated security functionality protects the contents of all memories. The logical Flash size can be configured in 1kB steps. The IC integrates coprocessors for AES, DES (both within the new Crypto2+ coprocessor) and a new 128 bit Public Key Crypto Coprocessor (Fame3) to support the implementation of asymmetric cryptographic algorithms.

**Note:** Please note that the Flash memory is also referred to as Non-Volatile Memory (NVM) in this Security Target.

The IC Embedded Software can either be located in ROM or Flash, see <u>Table 3</u>.

## 1.3.2 Software

The IC Dedicated Software comprises IC Dedicated Test Software for test purposes and IC Dedicated Support Software. The IC Dedicated Support Software consists of the Boot Software, which controls the boot process of the hardware platform. Furthermore, it

provides a Firmware Interface and optionally a Library Interface, simplifying access to the hardware for the Security IC Embedded Software. The IC Dedicated Support Software also comprises optional software components, i.e.,

- two logical cards (A and B),

- a System Mode OS which offers ready-to-use resource and access management for customer applications that do not want to be exposed to the more low-level features of the TOE,

- the System Mode OS also provides a Secure User Mode Box, which further restricts the access of code executed in User Mode (UM),

- a Flash Loader OS which supports download of code and data to Flash by the Composite Product Manufacturer before Operational Usage (e.g. during development), and

- a crypto library which provides simplified access to frequently used cryptographic algorithms AES, TDES, RNG, RSA, ECC, hashing and Utilities.

The availability of these software components depends on the different TOE configurations defined in Section 1.4.1.

#### 1.3.3 Documentation

The documentation includes a Product Data Sheet with several addenda, an Instruction Set Manual, a Guidance and Operation Manual, User Manuals for cryptographic functions and Utilities as well as a Wafer and Delivery Specification. This documentation comprises a description of the architecture, the secure configuration and usage of the IC hardware platform and the IC Dedicated Support Software by the Security IC Embedded Software. As some parts of the IC Dedicated Support Software are optional, the respective documentation is optional as well and depends on the TOE configurations chosen by the customer. The dependencies and list of documentation is given in Table 3.

# 1.3.4 Usage and major security functionality of the TOE

The security functionality of the TOE is designed to act as an integral part of a complete security system in order to strengthen the design as a whole. Several security mechanisms are completely implemented in and controlled by the TOE. Other security mechanisms allow for configuration by or even require support of the Security IC Embedded Software.

N7121 provides high security for smartcard applications and in particular for being used in the banking and finance market, in electronic commerce, or in governmental applications. Hence, the N7121 shall maintain

- the integrity and the confidentiality of code and data stored in its memories,

- the different TOE modes with the related capabilities for configuration and memory access, and

- the integrity, the correct operation and the confidentiality of security functionality provided by the TOE.

This is ensured by the construction of the TOE and its security functionality.

The N7121 basically provides a hardware platform and crypto library for an implementation of a smart card application with

functionality to calculate Data Encryption Standard (Triple-DES) with 112-bit or 168-bit keys,

- functionality to calculate Advanced Encryption Standard (AES) with different key lengths,

- functionality to calculate RSA, RSA key generation, RSA public key computation,

- functionality to calculate ECDSA (ECC over GF(p)) signature generation and verification, ECDSA (ECC over GF(p)) key generation, ECDH (ECC Diffie-Hellmann) key-exchange, and full point addition(ECC over GF(p)) over any Weierstrass curves from size 128 bits to size 640 bits with co-factor equal 1,

- basic support of the PACE protocol ([TR-03110-1], [TR-03110-2], [TR-03110-3], [TR-03110-4]) as ECC base-point operations are protected against leakage and fault injection,

- · KeyStore feature for secure key management,

- secure copy, move, and compare operations provided by the crypto library,

- functionality to compute SHA-1, SHA-224, SHA-256, SHA-384, and SHA-512,

- · a True Random Number Generator.

- a Hybrid Deterministic Random Number Generator.

- a Hybrid Physical Random Number Generator,

- a Physical Unclonable Function (PUF),

- · memory management control and memory encryption,

- · physical protection via sensors on the chip and chip shielding, and

- two completely separated logical cards A and B, each with System Mode and User Mode.

Further functionality of the TOE which does not correspond to security functionality as defined in this Security Target is

- ISO/IEC 7816 contact interface with UART and ISO/IEC 14443A contactless interface,

- a general purpose communication interface which can be used to directly access peripherals of the TOE.

- an Undocumented Function (UDF), i.e., a proprietary operation used for data blinding, and

- · cyclic redundancy check (CRC) calculation.

- KoreanSeed Library, providing cryptographic operations using the 128-bit block cipher SEED.

#### 1.3.5 **TOE** type

The TOE NXP Secure Smart Card Controller N7121 with IC Dedicated Software and Crypto Library, or in short N7121, is provided as IC hardware platform with IC Dedicated Software for various operating systems and applications with high security requirements.

# 1.3.6 Required non-TOE hardware/software/firmware

Besides the conventional communication interfaces, the TOE provides a general purpose I/O interface. It is not required to use this interface, however, it can be used to access major security features of the TOE. This certification does not address the communication via the general purpose I/O interface, however, the TOE implements countermeasures against misuse.

# 1.4 TOE description

# 1.4.1 Evaluated configurations and TOE components

The TOE features different types of memories, some are configurable to the customer others are fixed, as shown in the following table.

Table 2. Memories of the TOE

| Memory<br>type | Memory size                               | Description                                                                                                                   |

|----------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| NVM            | configurable up to 344 KBytes             | The size of the Non-Volatile Memory.                                                                                          |

| ROM            | Configurable to 0<br>KBytes or 150 KBytes | Size of the Read-Only Memory.                                                                                                 |

| RAM            | 12 KBytes                                 | Size of the Random-Access Memory. Size available to customer depends on ordered configuration (e.g., availability of MIFARE). |

The TOE provides different configuration options a customer can make in the ordering process (Ordering Configurations). The following table lists configurations with impact on the security functionality.

Default values are indicated as **bold text**.

**Table 3. TOE configuration options**

| Product option      | Choices                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ordering configu    | ırations                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NVM Size            | configurable in<br>1kB steps up to<br>344 KBytes | The Flash memory size is logically configurable, within the given step size.  Note: If utilized, the Flashloader occupies 16 kB of storage, which are freed up after its usage.                                                                                                                                                                                                                                                                                                                                                                                  |

| Customer Type       | System Mode customer     User Mode customer      | Depending on this choice, the customer has access to the System Mode of the logical card B (System Mode customer) or not (User Mode customer). In the first case, customers can store the Security IC Embedded Software in the System Mode of the logical card B. Otherwise, the NXP System Mode OS is placed on each available logical card in System Mode, while the customer can only access the less privileged User Mode.                                                                                                                                   |

| Use Flash<br>Loader | • Yes<br>• No                                    | Depending on this choice, the TOE provides the functionality of a Flash Loader such that customers can load their code to the NVM memory.  If the Flash Loader is available, the Library Interface and the N7121 Crypto Library become mandatory.  If the Flash Loader is not available, the customer can still decide whether the Security IC Embedded Software will be stored in ROM or Flash during the development process. The Security IC Embedded Software is then programmed to Flash by NXP and using the Flash Loader which will be removed afterward. |

Beside the above configurations, further Ordering Configurations are possible. However, these do not affect the Security Functionality defined in this ST. These configurations are listed below to provide a full picture:

Ordering Configurations without security impact:

- · User ID settings,

- · different options for contact-based and contactless communication,

- available data rates (106kbit/s, 106-848kbit/s, 106-848kbit/s and VHBR rates up to 3.2Mbit/s, or all),

- ATS/ATR check during testing.

- Enable or disable Chip Health Mode (CHM).

The TOE does not provide any functionality to tailor its available security functionality after delivery. Via Post-Delivery Configurations (PDC), the following configurations are possible which have no impact on the security functionality provided by the TOE:

- MIFARE DESFire EV2 (2K, 4K, 8K, 16K, 24K, 32K, or disabled) (resides in UM of card A) and

- MIFARE Plus EV1 (2K, 4K, or disabled) (resides in UM of card A).

#### Note:

Logical card A provides MIFARE DESFire and/or MIFARE Plus in its User Mode. The MIFARE Software does not provide any security functionality defined in this Security Target. The NXP SM OS is mandatory on Card A and cannot be replaced. It configures the Memory Management Unit in such a way that software running in User Mode of Card A cannot interfere with other software running on the TOE and related memories on the TOE if not explicitly allowed. This functionality is called "NXP Secure User Mode Box".

#### Note:

The CHM can be used for chip identification, application of post-delivery configurations, and functional self-tests of the TOE. If the CHM is not available, chip identification and post-delivery configurations is still available, however, a customer has to spend more effort to access the respective functionality. The functional self-tests which are available in the CHM are not part of the Security Functionality defined in this ST.

Depending on the customer choices, the N7121 comprises the following deliverables:

Table 4. TOE deliverables of the hard macro

| Туре                          | Name                                                                            | Release | Form of delivery                                                         |

|-------------------------------|---------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------|

| TOE components for a          | Ill configurations                                                              |         |                                                                          |

| IC Hardware                   | N7121                                                                           | B1      | Hard macro<br>instantiated within<br>a wafer, modules<br>and/or package. |

| IC Dedicated Test<br>Software | Test Software                                                                   | 9.2.3.0 | On-chip software                                                         |

| IC Dedicated Support          | Boot Software                                                                   | 9.2.3.0 | On-chip software                                                         |

| Software                      | Firmware                                                                        | 9.2.3.0 | On-chip software                                                         |

| Document                      | NXP Secure Smart Card Controller N7121  – Overview, Product data sheet [DSheet] | 3.3     | Electronic<br>document (PDF via<br>NXP DocStore)                         |

| Туре                             | Name                                                                                                                                           | Release | Form of delivery                                       |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------|

| Document                         | Product data sheet addendum [DSheet docume                                                                                                     |         | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Document                         | SmartMX3 family P71D321 Dedicated type creation, Product data sheet addendum [DSheet_OEF]                                                      | 3.1     | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Document                         | NXP Secure Smart Card Controller N7121  – Instruction Set Manual, Product data sheet addendum [DSheet_InSet]                                   | 3.0     | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Document                         | NXP Secure Smart Card Controller N7121  – Chip Health Mode, Product data sheet addendum [DSheet_CHM]                                           | 3.1     | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Document                         | NXP Secure Smart Card Controller N7121  – Peripheral Configuration and Use, Product data sheet addendum [DSheet_ Periph]                       | 3.2     | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Document                         | NXP Secure Smart Card Controller N7121  – MMU Configuration and NXP Firmware Interface Specification, Product data sheet addendum [DSheet_MMU] | 3.6     | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Document                         | NXP Secure Smart Card Controller<br>N7121, Information on Guidance and<br>Operation, Guidance and operation<br>manual [GOM]                    | 3.2     | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Document <sup>[1]</sup>          | NXP N7121 B1 Hardmarco - Lifecyle Documentation, Report [Lifecyle]                                                                             | 1.30    | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Deliverables of the Fla          | sh Loader OS                                                                                                                                   | ı       |                                                        |

| IC Dedicated Support Software    | Flashloader OS                                                                                                                                 | 1.2.5   | On-chip software                                       |

| Document                         | NXP Secure Smart Card Controller N7121  - Flashloader OS, Product data sheet addendum [DSheet_FL]                                              | 3.0     | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Deliverables of the Lib          | rary Interface                                                                                                                                 | 1       |                                                        |

| IC Dedicated Support<br>Software | Library Interface                                                                                                                              | 9.2.3.0 | On-chip software                                       |

| Library                          | Communication Library                                                                                                                          | 6.0.0   | Electronic files<br>(object files via<br>NXP DocStore) |

| Library                          | CRC Library                                                                                                                                    | 1.1.8   | Electronic files<br>(object files via<br>NXP DocStore) |

| Library                          | Memory Library                                                                                                                                 | 1.2.3   | Electronic files<br>(object files via<br>NXP DocStore) |

| Library                          | Flash Loader Library                                                                                                                           | 3.6.0   | Electronic files<br>(object files via<br>NXP DocStore) |

| Туре                          | Name                                                                                                      | Release     | Form of delivery                                            |

|-------------------------------|-----------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------|

| Document                      | NXP Secure Smart Card Controller N7121 – Shared OS Libraries, Product data sheet addendum [DSheet_LibInt] | 3.2         | Electronic<br>document (PDF via<br>NXP DocStore)            |

| Deliverables of the Sys       | stem Mode OS (for UM customers)                                                                           |             |                                                             |

| IC Dedicated Support Software | System Mode OS                                                                                            | 13.2.3.0    | On-chip software                                            |

| Document                      | NXP Secure Smart Card Controller N7121  – NXP System Mode OS, Product data sheet addendum [DSheet_SMOS]   | 3.5         | Electronic<br>document (PDF via<br>NXP DocStore)            |

| Deliverables for Card-        | A Developer (NXP) [2]                                                                                     |             | ,                                                           |

| Document                      | NXP Secure Smart Card Controller N7121, Specification and Design Documentation [Spec_and_Design]          | 1.0         | Electronic<br>document (PDF<br>via Internal NXP<br>network) |

| Deliverables of the cry       | pto library                                                                                               |             |                                                             |

| IC Dedicated Support Software | Crypto Library                                                                                            | 0.7.6       | On-chip software                                            |

| Package Random Nun            | nber Generation                                                                                           |             |                                                             |

| Library                       | RNG Lib                                                                                                   | 0.7.6       | Electronic files<br>(object files via<br>NXP DocStore)      |

| Library                       | RNG HealthTest Lib                                                                                        | 0.7.6       | Electronic files<br>(object files via<br>NXP DocStore)      |

| Document                      | N7121 Crypto Library – RNG Library,<br>User Manual [UM_RNG]                                               | 1.2         | Electronic<br>document (PDF via<br>NXP DocStore)            |

| Package Symmetric C           | iphers                                                                                                    |             | 1                                                           |

| Library                       | Sym. Cipher Lib                                                                                           | 0.7.6       | Electronic files<br>(object files via<br>NXP DocStore)      |

| Document                      | N7121 Crypto Library – Symmetric<br>Cipher Library (SymCfg), Preliminary user<br>manual [UM_SymCfg]       | 1.4         | Electronic<br>document (PDF via<br>NXP DocStore)            |

| Package KeyStore              |                                                                                                           |             | 1                                                           |

| Library                       | KeyStoreMgr Lib                                                                                           | 0.7.6       | Electronic files<br>(object files via<br>NXP DocStore)      |

| Document                      | N7121 Crypto Library – KeyStoreMgr<br>Library, User Manual [UM_KeyStore]                                  | 1.1         | Electronic<br>document (PDF via<br>NXP DocStore)            |

| TOE components requ           | ired for the packages Random Number Ger                                                                   | eration and | d Symmetric Ciphers                                         |

| Library                       | Sym. Utilities Lib                                                                                        | 0.7.6       | Electronic files<br>(object files via<br>NXP DocStore)      |

| Туре                              | Name                                                                                 | Release    | Form of delivery                                       |

|-----------------------------------|--------------------------------------------------------------------------------------|------------|--------------------------------------------------------|

| Document                          | N7121 Crypto Library – Utils Library, User Manual [UM_SymUtils]                      | 1.1        | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Package RSA En                    | cryption / Decryption                                                                |            |                                                        |

| Library                           | RSA Lib                                                                              | 0.7.6      | Electronic files<br>(object files via<br>NXP DocStore) |

| Document                          | N7121 Crypto Library – RSA Library, User Manual [UM_RSA]                             | 1.4        | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Package RSA Ke                    | y Generation                                                                         | 1          |                                                        |

| Library file                      | RSA Key Generation Lib                                                               | 0.7.6      | Electronic files<br>(object files via<br>NXP DocStore) |

| Document                          | N7121 Crypto Library – RSA Key<br>Generation Library, User Manual [UM_<br>RSAKeyGen] | 1.3        | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Package ECC ov                    | er GF(p)                                                                             |            |                                                        |

| Library                           | ECC Lib                                                                              | 0.7.6      | Electronic files<br>(object files via<br>NXP DocStore) |

| Document                          | N7121 Crypto Library – ECC over GF(p)<br>Library, User Manual [UM_ECC]               | 2.1        | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Package SHA                       |                                                                                      |            |                                                        |

| Library                           | SHA Library & Hash Library                                                           | 0.7.6      | Electronic files<br>(object files via<br>NXP DocStore) |

| Document                          | N7121 Crypto Library – SHA Library, User Manual [UM_SHA]                             | 1.1        | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Document                          | N7121 Crypto Library – HASH Library,<br>User Manual [UM_HASH]                        | 1.2        | Electronic<br>document (PDF via<br>NXP DocStore)       |

| TOE components<br>ECC over GF(p), | required for the packages RSA Encryption / Decand SHA                                | ryption, R | SA Key Generation,                                     |

| Library                           | Asym. Utilities Lib                                                                  | 0.7.6      | Electronic files<br>(object files via<br>NXP DocStore) |

| Document                          | N7121 Crypto Library – UtilsAsym Library,<br>User Manual [UM_AsymUtils]              | 1.3        | Electronic<br>document (PDF via<br>NXP DocStore)       |

| Package Koreans                   | Seed                                                                                 |            |                                                        |

| Library                           | KoreanSeed Lib                                                                       | 0.7.6      | Electronic files<br>(object files via<br>NXP DocStore) |

| Туре                                     | Name                                                                                      | Release | Form of delivery                                 |

|------------------------------------------|-------------------------------------------------------------------------------------------|---------|--------------------------------------------------|

| Document                                 | N7121 Crypto Library – KoreanSeed<br>Library, User Manual [UM_KoreanSeed]                 | 1.1     | Electronic<br>document (PDF via<br>NXP DocStore) |

| TOE components required for all packages |                                                                                           |         |                                                  |

| Document                                 | N7121 Crypto Library, Information on Guidance and Operation, Product user manual [GOM_CL] | 3.2     | Electronic<br>document (PDF via<br>NXP DocStore) |

<sup>[1]</sup> This guidance is available for NXP designers responsible for designing IO sidecar of a derived product only

#### Note:

Although the N7121 is considered self-sufficient at the boundary of the hard macro, its IC Dedicated Software might require instantiation specific functionality for the packaged product on top of the hard macro related functionality. These instantiation specific IC Dedicated Software relates to both, IC Dedicated Test Software and IC Dedicated Support Software. The instantiation specific IC Dedicated Software is defined by the Wafer Test version and the IC Dedicated Firmware extension ( see [DSheet\_MMU] and [DSheet\_SMOS]). Evaluated versions are given in Table 5 and Table 6.

Both release packages R1 and R2 consist of the deliverables given in Table 4 plus the instantiation specific IC Dedicated Software given in Table 5 (R1) and Table 6 (R2), respectively. It is important to note that, the release package R1 and R2 are only different in some functional improvements of IC Dedicated Software. There is no impact on the security functionalities claimed in this Security Target.

Table 5. Instantiation specific IC Dedicated Software for Release package R1

| ID of Wafer Test version | ID of the IC Dedicated Firmware extensions |

|--------------------------|--------------------------------------------|

| 0x83                     | 0x0                                        |

| 0x84                     | 0x0                                        |

| 0x90                     | 0x50                                       |

Table 6. Instantiation specific IC Dedicated Software for Release package R2

| ID of Wafer Test version | ID of the IC Dedicated Firmware extensions |

|--------------------------|--------------------------------------------|

| 0x85                     | 0x0                                        |

| 0x87                     | 0x1                                        |

| 0x92                     | 0x51                                       |

# 1.4.2 Physical scope of the TOE

The N7121 is manufactured in 40nm CMOS technology by GlobalFoundries and implemented as a hard macro. A block diagram of the IC hardware is depicted in Figure 1.

<sup>2]</sup> NXP develops and owns all code for Card-A. These deliverables are available for NXP only.

The N7121 consists of the IC hardware and IC Dedicated Software. The IC Dedicated Software is composed of IC Dedicated Test Software for test purposes and IC Dedicated Support Software. The IC Dedicated Support Software contains the Boot Software, the Firmware Interface, the Library Interface, the cryptographic libraries, the System Mode OS and the Flash Loader OS. All other software is called Security IC Embedded Software. The Security IC Embedded Software is not part of the TOE (Application Note 2 of [PP]).

Please note that not all parts of the IC are defined as TOE. In addition to the conventional contact-based and contactless communication interfaces, the TOE provides a general purpose I/O interface which is directly connected to the internal SFR bus. This interface can be connected to an I2C interface for instance which is not part of the evaluation. The Security Functionality of the TOE does not rely on the communication interface connected to this interface. However, the TOE implements countermeasures against misuse.

#### 1.4.3 Logical scope of the TOE

#### 1.4.3.1 Hardware description

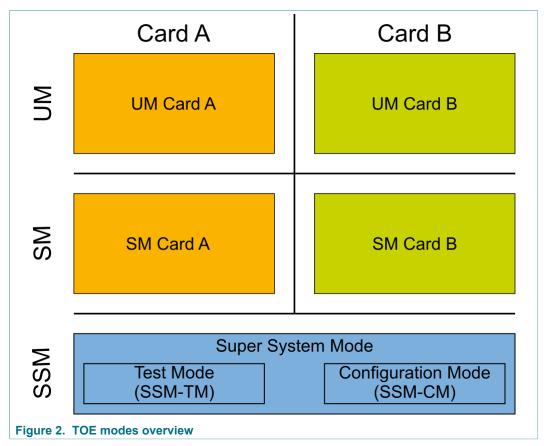

The TOE distinguishes different TOE modes as depicted in the following figure:

The Super-System Mode (SSM) is not available to the Security IC Embedded Software. It executes the Boot Software and Firmware.

The Test Mode (SSM-TM, short TM) and Configuration Mode (SSM-CM, short CM) have extended access rights compared to the Super-System Mode. The CPU however does not distinguish between SSM, TM, and CM. It only distinguishes between SSM, SM, and UM. In TM, the IC Dedicated Test Software is executed and is blocked before delivery. It includes the test operating system, test routines for the various blocks of the circuitry, control flags for the status of the Flash's manufacturer area and shutdown functions to ensure that security relevant test routing cannot be executed after Phase 3 of the life cycle defined in [PP]. Moreover, the IC Dedicated Test Software is used by NXP to download code related to System Mode or User Mode. A customer has no access to the IC Dedicated Test Software. The Configuration Mode is used to configure the TOE in the boot phase and to apply Post-Delivery Configurations.

The N7121 is able to control two different logical phases. After production of the Security IC, every start-up or reset completes with execution of the IC Dedicated Test Software. The test functionality is disabled at the end of the production test. Afterwards, every start-up or reset ends up in System Mode or User Mode, depending on the configuration 'Customer Type' selected by the customer.

The TOE further provides the System Mode (SM) and User Mode (UM) which are available for the IC Embedded Software. If both logical cards A and B are available, each card implements its own SM and UM, which are completely separated from each other. The NXP System Mode OS applies a pre-configuration of the MMU to guarantee this separation. If the NXP System Mode OS is not available (SM customer) the MMU has to be configured by the System Mode User, i.e., via the Security IC Embedded Software. In

case Logical Card A is not available, the TOE only distinguishes between UM, SM, and SSM (which includes TM and CM). The differentiation between both logical cards is only done via the MMU, the CPU only distinguishes between the different modes.

The System Mode has broader access to the hardware components available to the Security IC Embedded Software. The User Mode has restricted access to the CPU, specific Special Function Registers and the memories depending on the access rights granted by software running in System Mode. Please note that most Special Function Registers are implemented as RAM-based segment descriptors, initialized during start-up and controlled by the Memory Management Unit (MMU). The hardware components are controlled by the Security IC Embedded Software via Special Function Registers. Both are interrelated to the activities of the CPU, the Memory Management Unit, interrupt control, I/O configuration, NVM, timers and the coprocessors. A more detailed description of the Software available on and for the TOE is given in Section 1.4.3.2.

The N7121 provides interrupts. Interrupts force a jump to a specific fixed vector address in the ROM or Flash. Any interrupt can therefore be controlled and guided by a specific part of the Security IC Embedded Software. In addition, the TOE provides user calls and system calls. These calls have to be explicitly done by the Security IC Embedded Software via dedicated CPU instructions. A user call starts the execution of related code dedicated to one lower privileged mode (Super System Mode to System Mode or System Mode to User Mode). A system call starts the execution of related code dedicated to one higher privileged mode (User Mode to System Mode or System Mode to Super System Mode).

The Watchdog timer is intended to abort irregular program executions by a time-out mechanism and is enabled and configured by the Security IC Embedded Software.

The TOE incorporates Flash, RAM, and program memory available in ROM. Access control to all three memory types is enforced by a Memory Management Unit (MMU). The System Mode OS provides a simplification of the resource management (e.g. MMU firewall settings, dynamic segment setup, and peripheral access control). The MMU partitions each memory into several parts, defined as objects in the Access Control Policy (see Section 6.1.8).

The Triple-DES coprocessor supports single DES and Triple-DES operations. Only Triple-DES is in the scope of this evaluation, in 2-key or 3-key configurations, each 56-bit long (e.g., 112-bit or 168-bit key in total). The AES coprocessor supports AES operation with three different key lengths of 128, 192 or 256 bit. Both utilize the new Crypto2+ coprocessor. The physical random number generator provides true random numbers without pseudo random calculation. The new 128 bit Public Key Crypto Coprocessor (Fame3) supplies basic arithmetic functions to support the implementation of asymmetric cryptography, utilized by the asymmetric cryptographic library.

The TOE provides power saving modes with reduced activity. These are named IDLE Mode and SLEEP Mode, of which the latter one includes CLOCK STOP Mode.

The TOE protects secret data, which are stored on and operated by the TOE, against physical tampering. A memory encryption is added to the memories RAM, ROM and Flash such that data stored to these memories is encrypted. Chip shielding is added in form of active active shield. Light sensors are distributed over the chip area. Furthermore, the TOE is protected by voltage, temperature and frequency sensors. The security functionality of the IC hardware platform is mainly provided by the TOE, and completed by the Security IC Embedded Software. This causes dependencies between the security functionality of the TOE and the security functionality provided by the Security IC Embedded Software.

### 1.4.3.2 Software description

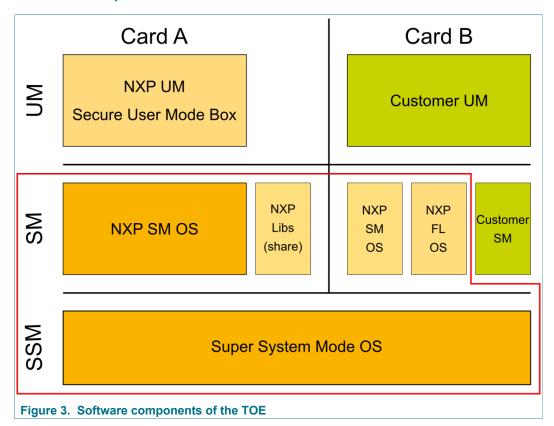

Figure 3 shows the different pieces of the available software on and for the TOE. The scope of the TSF is additionally highlighted by a red box. The TOE supports two logical cards (Card A and Card B). Both logical cards are divided into a User Mode and a System Mode. Operating system and applications of a Security IC are developed by the customers and included under the heading Security IC Embedded Software. The logical location of the Security IC Embedded Software depends on the usage of the IC hardware platform. For User Mode customers, it is stored in the memories which belong to the User Mode of Card B. For System Mode customers, the Security IC Embedded Software can also be stored in memories which belong to the System Mode of Card B. Logical Card A is available for NXP code only. If this logical card is available, the SM of card A contains the NXP SM OS while User Mode of Card A contains NXP code like MIFARE Plus or MIFARE DESFire.

The separation between the two logical cards (Card A and Card B) is provided by the socalled "Vertical IP firewall" which allows for having two completely separated logical cards on the same hardware without any unintended impact on each other. Because a logical card is also divided into a User Mode and a System Mode, it is possible to offer a security feature called "Secure User Mode Box".

This feature is of special importance as it allows for the integration of data and code to a certified product without any security impact. The Secure User Mode Box restricts the access rights for code running in UM of Card A, such that it has no influence on other modes and cards. For the "Secure User Mode Box", a fixed set of access rights are NXP-defined during production. The NXP System Mode OS does not provide any interfaces to the UM to change these access rights.

For logical card B, a "Secure User Mode Box" can be implemented as well. However, in this case the configuration of the User-Mode access rights is up to the customer and therefore out of the scope of this certification. This configuration is done as part of the ordering process.

Using shared memory segments it is possible to share data or code between the separated logical cards. The owner of a memory block has to explicitly allow this kind of sharing. The libraries are shared between the logical cards using this mechanism, reducing the footprint, as code only has to be present on the device once. An inter-card communication mechanism allows the currently active card to send a message to the inactive card with a request for card switching. This mechanism allows for the handover of execution between the logical cards.

The IC Dedicated Test Software is developed by NXP. It includes the test operating system, test routines for the various blocks of the circuitry, control flags for the status of the Flash's manufacturer area and shutdown functions to ensure that security relevant test routines cannot be executed illegally after Phase 3. The IC Dedicated Test Software is stored in ROM memory segments which belong to the Super-System Mode (SSM-TM).

The IC Dedicated Support Software comprises the following parts:

- The Boot Software is executed after each reset of the TOE, i.e. every time when the TOE starts. It sets up the TOE and does some basic configuration of the hardware based on the settings stored in memories assigned to the SSM.

The Boot Software is stored in ROM memories assigned to the SSM.

- 2. The Firmware Interface is stored in memories assigned to the SSM. It provides low-level flash management, the Post-Delivery Configuration feature and basic system functionality like self-testing, error-counter handling, PUF and reset functionality. Notice, that Boot Software and IC Dedicated Test Software also access the Firmware Interface. The 'one-time executed' part of the Firmware Interface (for instance PDC) is located in FLASH, the remaining parts are located in ROM.

- 3. The NXP System Mode OS is an Operating System developed by NXP. In general, the NXP System Mode OS provides a ready-to-use resource and access management for any customer application and does not expose the more low-level features, such as MMU configuration. It provides the feature of the Secure User-Mode Box.

- The NXP System Mode OS is a mandatory component of Card A, implementing its System Mode OS. It is responsible for sharing the different TOE libraries available. For System Mode customers who do not need any TOE library, the Flash Loader, or any NXP application running in User Mode of Card A, the System Mode OS on Card A is deactivated and cannot be executed. This results in the deactivation of Card A. For Card B the NXP System Mode OS is an optional component. However, it becomes mandatory for User Mode customers.

- The NXP System Mode OS can be stored in ROM or FLASH.

- 4. The Library Interface is an optional module and can be stored in any Card and mode. It provides simplified communication, CRC and memory functions to the Security IC Embedded Software. The Library Interface is required by the Flashloader OS and the Crypto Libraries.

- 5. The crypto library is an optional library which provides extended functionality and access to the following functionality to the Security IC Embedded Software:

- · Package Symmetric Ciphers for AES and TDES in various modes.

- Package Random Number Generation which implements the hybrid deterministic RNG and hybrid physical RNG including health tests.

NXP Secure Smart Card Controller N7121

- Package RSA Encryption / Decryption: RSA encryption, decryption and signature generation with key sizes from 1976 and up to 4096 bits. Key sizes from 512 bits and less than 1976 bits are also supported but not in the scope of evaluation.

- Package RSA Key Generation: Generation of RSA key pairs and public key computation with key sizes from 1976 and up to 4096 bits. If FIPS compliance is enforced, only key sizes from 2048 to 3072 bits are supported. Key sizes from 512 bits and less than 1976 bits are also supported but not in the scope of evaluation.

- Package ECC over GF(p):

- The ECDSA (ECC over GF(p)) algorithm can be used for signature generation and signature verification.

- The ECDSA (ECC over GF(p)) key generation algorithm can be used to generate ECC over GF(p) key pairs for ECDSA.

- The ECDH (ECC Diffie-Hellman) key exchange algorithm can be used to establish cryptographic keys. It can be also used as secure point multiplication.

- Provide secure point addition for Elliptic Curves over GF(p).

- Provide curve parameter verification for Elliptic Curves over GF(p).

- The TOE supports various key sizes for ECC over GF(p) up to a limit of 640 bits for signature generation, key pair generation and key exchange. For signature verification the TOE supports key sizes up to a limit of 640 bits.

- · Package SHA:

- The SHA-1, SHA-224, SHA-256, SHA-384, and SHA-512 algorithms can be used for different purposes such as compute hash values in the course of digital signature creation and key verification.

- The crypto library implements the KeyStore feature for a secure key management in RAM (see Section 7.2.2.2 for details).

- The crypto library further implements secure move, copy, and compare operations.

Even though the TOE does not implement the full PACE protocol, it provides basic support for the implementation of this protocol in the IC Embedded Software via these secure operations.

- 6. The Flashloader OS is an optional module and stored in a memory segments assigned to SM of Logical Card B and cannot be directly accessed by the Security IC Embedded Software. It is located in ROM and FLASH. One-time executed code is located in FLASH and is removed after use. The freed up memory is then available for the Security IC Embedded Software.

- The Flashloader OS supports the download of code and data to Flash by the Composite Product Manufacturer before Operational Usage (e.g. during development). This functionality can be made unavailable after usage. When the Flashloader OS module is available, the Library Interface, the N7121 Crypto Library and the System Mode OS become mandatory. All logical dependencies of the IC Dedicated Support Software are described in the definitions above.

**Note:** Both cryptographic libraries are provided as a library rather than as a monolithic program, and hence a user of the library may include only those functions that are actually required – it is not necessary to include all cryptographic functions of the library in every Security IC Embedded Software. For this purpose, Table 4 defines different packages of the crypto libraries which can be included in the customer application. For example, it is possible to use the package ECC over GF(p) only in case of the N7121 Crypto Library. The inter-dependencies of the different packages are resolved in Table 4.

With respect to Application note 32 of the [PP], the physical location of the Security IC Embedded Software can be either in ROM or in Flash. The Security IC Embedded Software itself is not in the scope of this evaluation.

All logical dependencies of the IC Dedicated Support Software are described in the definitions above.

# 1.4.4 Security during Development and Production

The Security IC product life-cycle is scheduled in phases as introduced in [PP]. IC Development as well as IC Manufacturing and Testing, which are Phases 2 and 3 of the life-cycle, are part of the evaluation. Phase 4 the IC Packaging is also part of the evaluation. The Security IC is delivered at the end of Phase 3 or Phase 4 in the life-cycle (Application Note 1 of [PP]). The development and production environment of the TOE ranges from Phase 2 to TOE Delivery.

With respect to Application Note 3 in [PP] the TOE supports the authentic delivery using the FabKey feature. For further details refer to the data sheet [DSheet] and the guidance and operation manual [GOM].

During the design and the layout process only personnel involved in the specific development project for an IC have access to sensitive data. Different teams are responsible for the design data and for customer related data. The production of wafers includes two different steps regarding the production flow. In the first step the wafers are produced with the fixed masks independent of the NCN or CCN. After that step the wafers are completed with the product type specific data, including ROM and Flash Code, and data (if applicable) as identified by NCN and CCN. The test process of every die is performed in CC certified test centers. Delivery processes between the involved sites provide accountability and traceability of the TOE. The TOE is provided in form of sawn wafers, modules, inlays or packages depending on the individual commercial type.

# 1.4.5 TOE intended usage

The end-consumer environment of the TOE is Phase 7 of the Security IC product lifecycle as defined in [PP]. In this phase the Security IC product is in usage by the end-consumer. Its method of use now depends on the Security IC Embedded Software. The Security ICs including the TOE can be used to perform various functions in a wide range of applications. Examples are identity cards, Banking Cards, Pay-TV, Health cards and Transportation cards. The end-user environment covers a wide spectrum of very different functions, thus making it difficult to monitor and avoid abuse of the TOE. The TOE is intended to be used in an insecure environment, which does not protect against threats.

The device is developed for high-end safeguarded applications, and is designed to be suited for embedding into chip cards with various possible communication interfaces, for example ISO/IEC 7816, contactless applications according to ISO/IEC 14443 or others. Usually a Security IC (e.g. a smartcard) is assigned to a single individual only, but it may also be used by multiple applications in a multi-provider environment. Therefore the TOE might store and process secrets of several systems, which must be protected from each other. The TOE then must meet security requirements for each single security module.

Secret data shall be used as input for calculation of authentication data, calculation of signatures and encryption of data and keys.

In development and production environment of the TOE the Security IC Embedded Software developer and system integrators such as the terminal software developer may use samples of the TOE for their testing purposes. It is not intended that they are able to change the behavior of the Security IC in another way than an end-consumer. The user environment of the TOE ranges from TOE delivery to Phase 7 of the Security IC product life-cycle, and must be a controlled environment up to Phase 6.

**Note:** The TOE can be delivered as a stand-alone security IC with deactivated GPIO interface or as a certified component of a product that contains a sidecar connecting to the TOE's interface wirings. If GIPO is available as an external interface of the TOE, no security relevant data must be processed, or must be protected by means that is outside the scope of the TOE. In case the GPIO is deactivated, the deactivation mechanism is protected by physical countermeasures like shielding, redundancy and sensors.

**Note:** Please note that the phases from TOE Delivery to Phase 7 of the Security IC Product life-cycle are not part of the TOE construction process in the sense of this Security Target. Information about these phases is just included to describe how the TOE is used after its construction. Nevertheless such security functionality of the TOE, that is independent of the Security IC Embedded Software, is active at TOE Delivery and cannot be disabled by the Security IC Embedded Software in the following phases.

**Note:** Additionally, it is important to note that, the integration of the TOE, that is the hard macro, resulting in the final product is done within the premise of NXP and inside its secure IT environment only.

**Note:** Finally, any side-car which is potentially developed outside of the NXP's secure development network must be merged with the hardmacro inside NXP's secure development network. The hardmacro design details of the hardmacro will not be provided to any external party.

#### 1.4.6 Interface of the TOE

The electrical interface of the N7121 are the pads to connect the lines power supply, ground, reset input and clock input. The TOE provides a general purpose I/O interface which allows direct access to the internal SFR bus. This is an external interface that can be used to connect an I2C interface for instance without affecting the certification.

The TOE implements conventional contact-based and contactless interfaces (ISO/IEC 7816 contact interface with UART and ISO/IEC 14443A contactless interface). The availability of these interfaces depends on the actual configuration of the TOE.

The logical interface of the TOE depends on the CPU mode and the associated software.

- Upon every start-up the Boot Software is executed in Super System Mode. This

software initializes and configures the TOE. This comprises the selection of IC

Dedicated Test Software (before TOE delivery) and of Security IC Embedded Software

(after TOE delivery). Only in case the configuration option 'Enable Chip Health Mode'

is enabled, starting of built-in self-test routines and read-out of TOE identification items

is supported. If this configuration option is disabled, the Boot Software provides no

interface. In this case there is no possibility to interact with this software.

- Before TOE delivery the logical interface is defined by the IC Dedicated Test Software.

This IC Dedicated Test Software is executed in Super System Mode and comprises

the test operating system used for production testing. IC Dedicated Test Software is

embedded in the Test Software.

- In System Mode and User Mode (after TOE Delivery) the software interface is the

set of instructions, the bits in the special function registers that are related to these

modes and the physical address map of the CPU including memories. The access to

the special function registers as well as to the memories depends on the TOE mode

configured by the Security IC Embedded Software.

**Note:** The logical interface of the TOE that is visible on the electrical interface after TOE Delivery is based on the Security IC Embedded Software developed by the software

developer. The identification and authentication of the user in System Mode or User Mode must be controlled by the Security IC Embedded Software.

**Note:** The chip surface can be seen as an interface of the TOE, too. This interface must be taken into account regarding environmental stress e.g. like temperature and in the case of an attack, for which the attacker manipulates the chip surface.

**Note:** An external voltage and timing supply as well as a logical interface are necessary for the operation of the TOE. Beyond the physical behavior of the logical interface is defined by the Security IC Embedded Software.

# 2 Conformance claims

This Security Target claims to be conformant to the Common Criteria version 3.1:

- Common Criteria, Part 1: Common Criteria for Information Technology Security Evaluation, Part 1: Introduction and general model, Version 3.1, Revision 5, April 2017, CCMB-2017-04-001. [CC Part1]

- Common Criteria, Part 2: Common Criteria for Information Technology Security Evaluation, Part 2: Security functional components, Version 3.1, Revision 5, April 2017, CCMB-2017-04-002. [CC\_Part2]

- Common Criteria, Part 3: Common Criteria for Information Technology Security Evaluation, Part 3: Security assurance components, Version 3.1, Revision 5, April 2017, CCMB-2017-04-003. [CC\_Part3]

For the evaluation the following methodology will be used:

Common Methodology for Information Technology Security Evaluation, Evaluation Methodology, Version 3.1, Revision 5, April 2017, CCMB-2017-04-004. [CEM]

This Security Target claims to be **CC Part 2 extended** and **CC Part 3 conformant**. The extended Security Functional Requirements are defined in <u>Section 5</u>.

# 2.1 Package claim

This Security Target claims conformance to the assurance package EAL6 augmented. The augmentations to EAL6 is ALC\_FLR.1. In addition, the Security Target is augmented using the component ASE\_TSS.2, which is chosen to include architectural information on the security functionality of the TOE.

The level of evaluation and the functionality of the TOE are chosen in order to allow the confirmation that the TOE is suitable for use within devices compliant with the German Digital Signature Law.

**Note:** The Protection Profile (PP) "Security IC Platform Protection Profile with Augmentation Packages" [PP] to which this Security Target claims conformance (refer to Section 2.2) requires assurance level EAL4 augmented. The changes, which are needed for EAL6, are described in the relevant sections of this Security Target.

#### 2.2 PP claim

This Security Target claims strict conformance to the Protection Profile (PP):

Security IC Platform Protection Profile with Augmentation Packages, Version 1.0, registered and certified by Bundesamt für Sicherheit in der Informationstechnik (BSI) under the reference BSI-PP-0084-2014 [PP].

Thus, the concepts are used in the same sense. For the definition of terms refer to [PP]. This chapter does not need any supplement in the Security Target.

This conformance claim includes the following packages of security requirements out of those for Loader defined in the Protection Profile:

- Package "Package 1: Loader dedicated usage in Secured Environment only" Conformant and

- Package "Package2: Loader dedicated for usage by authorized users only" Conformant.

NXP Secure Smart Card Controller N7121

This conformance claim includes the following packages of security requirements out of those for Cryptographic Services defined in the Protection Profile [PP]:

- Package "TDES" Conformant and

- Package "AES" Conformant.

If the respective package of the crypto library is available, the additional functionality results in the following change to the conformance claim:

- · Package "TDES" Augmented and

- Package "AES" Augmented.

Furthermore, if the respective package of the crypto library is available, the additional functionality results in the inclusion of the following conformance claim:

· Package "Hash functions" Conformant.

The TOE provides additional functionality, which is not covered in [PP]. In accordance with Application Note 4 of [PP] this additional functionality is added using the policy P.Add-Components and P.Add-Crypto-Func (see Section 3.3).

### 2.3 Conformance claim rationale

According to Section 2.2 this ST claims strict conformance to [PP].

The TOE type defined in Section 1.3.5 is a smartcard controller with IC Dedicated Software. This is consistent with the TOE definition for a Security IC in Section 1.2.2 of [PP]. The sections within this document where Security Problem Definitions, Security Objectives and Security Functional Requirements (SFR) are defined, clearly state which of these items are taken from the Protection Profile and which are added in this Security Target. Moreover, all additionally stated items in this Security Target do not contradict the items included from the PP (see the respective sections in this document). The operations done for the SFRs taken from the PP are also clearly indicated.

The evaluation assurance level claimed for this TOE is shown in <u>Section 6.2</u> to include respectively exceed the requirements claimed by the PP (EAL4+).

These considerations show that the Security Target correctly claims conformance to [PP].

# 3 Security problem definition

This chapter lists the assets, threats, assumptions and organizational security policies from [PP] and describes extensions to these elements in detail.

# 3.1 Description of assets

All assets, which are defined in Section 3.1 of the [PP], are related to standard functionality. They are applied in this Security Target. These assets are:

- integrity and confidentiality of User Data stored and in operation,

- integrity and confidentiality of Security IC Embedded Software, stored and in operation,

- correct operation of the Security Services provided by the TOE for the Security IC Embedded Software, and

- · random numbers.

To be able to protect these assets the TOE shall protect its Security Functionality. Therefore critical information on the TOE shall be protected. Critical information includes:

- · logical design data, physical design data, IC Dedicated Software, as well as

- initialization data and pre-personalization data, Security IC Embedded Software, specific development aids, test and characterization related data, material for software development support, and photo masks.

**Note:** Note that the keys for cryptographic calculations using security services of the TOE are treated as User Data.

# 3.2 Threats

The Threats defined in Protection Profile are used for this ST without change. Therefore, see [PP] for their definitions. A complete list of Threats defined in [PP] is given in the following table:

Table 7. Threats defined in Protection Profile

| Name                | Title                                   |

|---------------------|-----------------------------------------|

| Name                | Title                                   |

| T.Leak-Inherent     | Inherent Information Leakage            |

| T.Phys-Probing      | Physical Probing                        |

| T.Malfunction       | Malfunction due to Environmental Stress |

| T.Phys-Manipulation | Physical Manipulation                   |

| T.Leak-Forced       | Forced Information Leakage              |

| T.Abuse-Func        | Abuse of Functionality                  |

| T.RND               | Deficiency of Random Numbers            |

In compliance with Application Note 4 in [PP], the TOE provides additional functionality to protect against threats that appear when the TOE is used for multiple applications.

The TOE provides the Security IC Embedded Software running in System Mode with control of access to memories and hardware components by different applications running in User Mode. In this context, User Data of different applications is stored to such memory and processed by such hardware components. The Security IC Embedded Software controls all these User Data. Any access to User Data assigned to one

application by another application contradicts separation between different applications and is considered as a threat.

The TOE shall avert the threat T.Unauthorised-Access as specified below.

#### T.Unauthorised-Access

# **Unauthorized Memory or Hardware Access**

#### Adverse action:

An attacker may try to read, modify or execute code or data stored in restricted memory areas. An attacker may try to access or operate hardware resources that are restricted by executing code that accidentally or deliberately accesses these restricted hardware resources. Any code executed or data used in System Mode or User Mode may accidentally or deliberately access code or User Data of other applications. Any code executed or data used in System Mode or User Mode may accidentally or deliberately access hardware resources that are restricted to other applications

Threat agent:

Attacker having high attack potential and access to the

TOE.

Asset:

Code executed by and data belonging to the IC Dedicated Support Software running in Super System Mode or Test Mode as well as code executed by and data belonging to the Security IC Embedded Software.

**Application Note:**

In case the NXP System Mode OS is available, this Threat also covers an attacker who may try to use malicious code placed in the User Mode of Card A or B to modify the correct behavior of the IC Dedicated Software or the Security IC Embedded Software as well as read or modify code or data belonging to the Security IC Dedicated Software or the Security IC Embedded Software.

#### **T.Malicious-UM-Application**

#### Malicious code running in UM of Card A (optional)

Adverse action:

An attacker may try to use malicious code placed in User Mode of logical card A to modify the correct behavior of the Security IC Dedicated Software or the Security IC Embedded Software as well as read or modify code or data belonging to the Security IC Dedicated Software or the Security IC Embedded Software.

Threat agent

Attacker having high attack potential and access to the

TOE.

Asset:

Code executed by and data belonging to the the Security IC Dedicated Software and the Security IC Embedded

Software.

## **Application Note:**

This threat is only applicable if the logical card A is available.

Restrictions of access to memories and hardware resources, which are available to the Security IC Embedded Software, must be defined and implemented by the security policy of the Security IC Embedded Software based on the specific application context.

# 3.3 Organizational security policies

The Security Policies defined in [PP] are used for this ST without change. Therefore, see [PP] for their definitions. A complete list of Threats defined in [PP] is given in the following table:

Table 8. Security policies defined in the Protection Profile

| Name               | Title                                                |  |

|--------------------|------------------------------------------------------|--|

| P.Process-TOE      | Identification during TOE Development and Production |  |

| P.Lim_Block_Loader | Limiting and Blocking the Loader Functionality       |  |

| P.Ctlr_Loader      | Controlled usage to Loader Functionality             |  |

| P.Crypto-Service   | Cryptographic services of the TOE                    |  |

In compliance with Application Note 5 in the [PP], this Security Target defines additional security policies as detailed below.

The TOE provides specific security functionality, which can be used by the Security IC Embedded Software. This specific security functionality is not derived from threats identified for the TOE. Instead, the Security IC Embedded Software decides how to use this security functionality to protect from threats for the composite product. Thus, security policy P.Add-Components is defined as follows.

#### **P.Add-Components**

#### **Additional Specific Security Components**

The TOE shall provide the following additional security functionality to the Security IC Embedded Software:

- · self-tests, and

- integrity support of data stored to NVM.

# P.Add-Crypto-Func

#### Additional Cryptographic Functionality (optional)

The TOE shall provide the following additional cryptographic functionality to the Security IC Embedded Software:

- · PUF functionality,

- RSA encryption, decryption, signature generation, signature verification, message encoding and signature encoding,

- RSA public key computation,

- · RSA key generation,

- ECDSA (ECC over GF(p)) signature generation and verification,

NXP Secure Smart Card Controller N7121

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved

- ECC over GF(p) key generation,

- ECDH (ECC Diffie-Hellmann) key exchange,

- ECC over GF(p) point addition,

- ECC over GF(p) curve parameter verification.

**Note:** This policy depends on the TOE configuration and the availability of the N7121 Crypto Library.

# 3.4 Assumptions

All assumptions defined in Section 3.4 of [PP] are valid for this Security Target:

Table 9. Assumptions defined in the Protection Profile

| Name             | Title                                                      |  |

|------------------|------------------------------------------------------------|--|

| A.Process-Sec-IC | Protection during Packaging, Finishing and Personalisation |  |

| A.Resp-Appl      | Treatment of user data of the Composite TOE                |  |

In compliance with Application Notes 6 and 7 of [PP], this Security Target defines two additional assumptions as follows.

#### A.Check-Init

#### Check of initialization data by the Security IC Embedded

The Security IC Embedded Software must provide a function to check initialization data. Such data is defined by the Composite Product Manufacturer and injected by the TOE Manufacturer into the non-volatile memory to provide the ability to identify and trace the TOE.

#### A.Key-Function

# **Usage of Key-dependent Functions**

Key-dependent functions (if any) shall be implemented in the Security IC Embedded Software in a way that they are not susceptible to leakage attacks (as described under T.Leak-Inherent and T.Leak-Forced).

**Note:** Note that here the routines which may compromise keys when being executed are part of the Security IC Embedded Software. In contrast to this the threats T.Leak-Inherent and T.Leak-Forced address (i) the cryptographic routines which are part of the TOE and (ii) the processing of User Data including cryptographic keys.

# 4 Security objectives

# 4.1 Security objectives of the TOE

All Security Objectives of the TOE, which are defined in [PP] are applied to this Security Target. This also comprises the Security Objectives defined in the functional packages which are claimed in Section 2.2. The following table lists these Security Objectives of the TOE:

Table 10. Security objectives of the TOE defined in the Protection Profile

| Name                          | Title                                           |  |

|-------------------------------|-------------------------------------------------|--|

| O.Leak-Inherent               | Protection against Inherent Information Leakage |  |

| O.Phys-Probing                | Protection against Physical Probing             |  |

| O.Malfunction                 | Protection against Malfunctions                 |  |

| O.Phys-Manipulation           | Protection against Physical Manipulation        |  |

| O.Leak-Forced                 | Protection against Forced Information Leakage   |  |

| O.Abuse-Func                  | Protection against Abuse of Functionality       |  |

| O.Identification              | TOE Identification                              |  |

| O.RND                         | Random Numbers                                  |  |

| O.Cap_Avail_Loader            | Capability and availability of the Loader       |  |

| O.Ctrl_Auth_Loader (optional) | Access control and authenticity for the Loader  |  |

| O.TDES                        | Cryptographic service Triple-DES                |  |

| O.AES                         | Cryptographic service AES                       |  |

| O.SHA (optional)              | Cryptographic service Hash functions            |  |

The objective O.Ctrl\_Auth\_Loader depends on the current state of the Flash Loader. In case the Flash Loader is blocked (after usage or as the Flash Loader is deactivated following Table 3), the respective functionality is not available anymore. The objectives O.AES and O.TDES depend on the availability of the AES and DES coprocessor which can be deactivated following Table 3.

In compliance with Application Notes 8 and 9 of [PP], additional Security Objectives for the TOE are defined below based on additional functionality provided by the TOE.

#### O.NVM-Integrity

## **Integrity Support of data stored to NVM**

The TOE shall provide detection and correction of failures in NVM memories to support integrity of contents stored there.

# **O.Access-Control**

# Access Control to Memories and Special Function Registers

The TOE shall control access of CPU instructions to memory areas depending on memory partitioning by the MMU and based on the CPU modes Super System Mode, System Mode and User Mode. In Super System Mode, System Mode and User Mode, the TOE shall

control access also based on configuration. In User Mode, the TOE shall control access also based on memory segments, which are configured in System Mode when implementing a memory management scheme. This control shall be individual to each memory segment and consider different access rights.

The only way to change the TOE mode shall be restricted as well. The change to a higher or less privileged mode shall be done by using explicit instructions or by interrupts triggered by hardware peripherals of the TOE. The TOE shall further provide mechanisms to return to the previous mode.